The AHB TFT LCD Controller is a configurable core that interfaces to an AHB or generic microprocessor bus and provides all the timing control and pixel serialization for controlling various TFT LCD Display Panels. The core can also be used with various RAMDACs to interface to VGA Monitors or VGA style LCD Panels.

The AHB TFTLCD Controller supports 24-bit true color and 16-bit color, as well as an 8-bit color display mode via the 256-Pixel Palette Ram. A 24-bit true color multiplex mode is also supported in which 3 8-bit sub-pixels are time-multiplexed (R, G, B) on an 8-bit output. Pixel clock generation, Sync Control and Display Enable controls are fully programmable and can be used with a wide range of system clock rates.

The LCD data interface contains 8-bit Red, 8-bit Green, and 8-bit Blue for a total of 24-bits. The LCD data interface will work with 6-bit RGB panels as well.

Interrupt sources timed to hsync, vsync and control signals are programmable and selectable to signal the processor to update display information.

The AHB TFTLCD supports an asynchronous clock input (lcdClk) as a timebase for pixel operations.

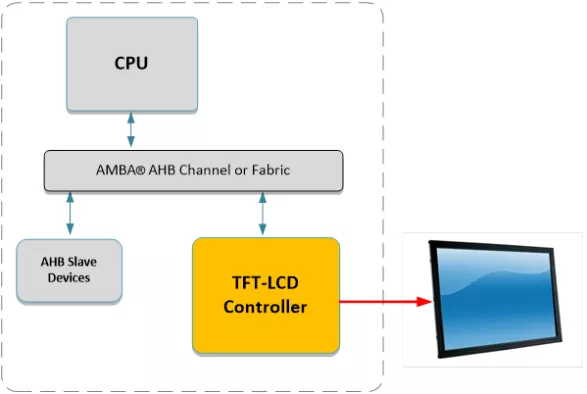

AHB TFT LCD Controller

Overview

Key Features

- 24-bit TFT LCD Controller

- 16 x 32-Pixel FIFO

- 256-Pixel Palette Mode

- True Color and 24-bit Color support

- Programmable Hsync and Vsync rates

- Supports up to 1024 x 768 resolution

- Pixel DMA controller

- Programmable Interrupt Interface

- Supports wide variety of system clock rates

Block Diagram

Deliverables

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

- C-Sample Code

Technical Specifications

Maturity

Silicon Proven

Availability

Now