400MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

Overview

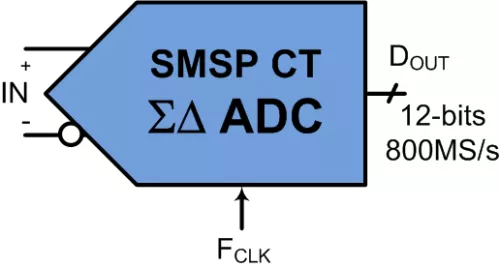

The SM-CTDSM-400M is a 12-bit continuous-time delta-sigma (CT??) analog-to-digital converter IP. By leveraging Seamless’ patented Switched-Mode Signal Processing (SMSP) technology, our ADC seamlessly fits into system-on-chip integrated circuits requiring only small area and low power. With up to 400MHz input signal bandwidth, 60dB of SNDR, high clock jitter tolerance and a resistive input, SM-CTDSM-400M’s over-sampling architecture is extremely well suited for high-speed transceivers and LiDAR applications.

Key Features

- 60dB SNDR

- Continuous-time ?? ADC

- High clock jitter tolerance

- Background PVT Cal

- Low-power

- Automotive temperature grade

- Resistive Input Impedance

- Power-down mode

Benefits

- Our patented Si-proven Switched-Mode Signal Processing (SMSP) technology overcomes the many challenges of designing high-performance analog and mixed-signal circuits in deep submicron processes, by leveraging the available fast transistors, enabling the fastest and lowest power analog and mixed-signal circuits in scaled CMOS technologies.

Block Diagram

Applications

- 5G communication systems, imaging and LiDAR

Deliverables

- GDSII

- LEF Abstract

- Behavioral Verilog-VAMS

- Liberty.lib

- Integration guide

Technical Specifications

Foundry, Node

28nm, 16nm, 14nm TSMC/GF

Maturity

Pre-Silicon

Related IPs

- 800MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 40MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 80MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 45MHz, 15-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 250MHz, 12-bit High Speed Delta Sigma ADC for 5G, LiDAR and Imaging

- 250MHz Multi-channel High Speed Analog Front-End (AFE) for LiDAR, 5G and imaging