The main PCI-T32 Interface core purpose is to isolate the user from having to solve complex problems of the PCI interface implementation and let the user instead focus on the application development.

The PCI-T32 Interface supports 32-bit address/data bus and operates up to 33 MHz (66 MHz optional) PCI clock frequency. It is fully compliant with the PCI Local Bus Specification, Revision 2.3.

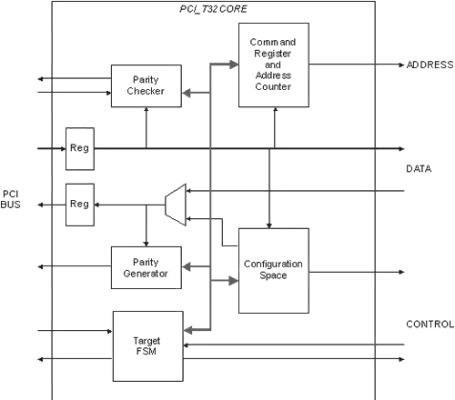

The PCI-T32 Interface is a Target–only PCI Interface core. The interface implements 64 bytes of PCI Configuration Space registers. It is possible to extend the Configuration Space up to 256 bytes if required.

The Target supports up to six Base Address Registers with both I/O and Memory space decoding from 16 bytes up to 4 GB.

The Target supported commands are:

Configuration Read, Configuration Write

Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL), Memory Write and Invalidate (MWI)

I/O Read, I/O Write

This core can be mapped to any any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available.

32-bit, 33 MHz PCI Target Interface Core

Overview

Key Features

- PCI specification 2.3 compliant

- 33 MHz performance (66MHz optional)

- 32-bit datapath

- Zero wait states burst mode

- Full Target functionality

- Single interrupt support

- Type 0 Configuration space

- Support of all Base Address Registers

- Support of backend initiated target retry, disconnect and abort

- Parity generation and parity error detection

- Optional bridge / interface to AMBA/AHB or Avalon-MM

- Available in synthesizable HDL source code or as targeted FPGA netlist

Block Diagram

Applications

- PCI I/O communication boards

- PCI Data Acquisition Boards

- Embedded system PCI applications

Deliverables

- HDL RTL source code (ASICs) or post-synthesis EDIF netlist (FPGAs)

- Sophisticated HDL Testbench

- Simulation script, vectors, expected results, and comparison utility

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications and a system integration guide

Technical Specifications

Maturity

Production Proven

Availability

Now