Agentic AI-based Coverage Closure for Formal Verification

By Sivaram Pothireddypalli 1, Ashish Raman 2, Deepak Narayan Gadde 3, Aman Kumar 1

1 Infineon Technologies India Private Limited, India

2 Dr. B R Ambedkar National Institute of Technology Jalandhar, India

3 Infineon Technologies Dresden AG & Co. KG, Germany

Abstract

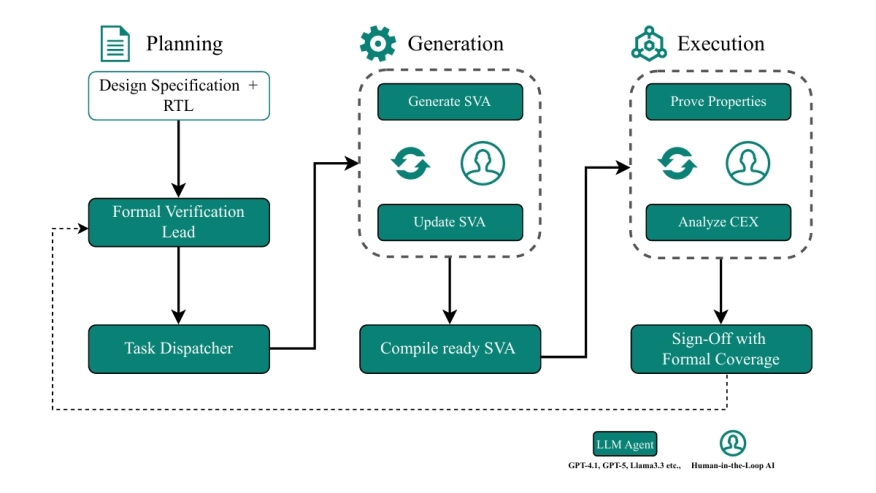

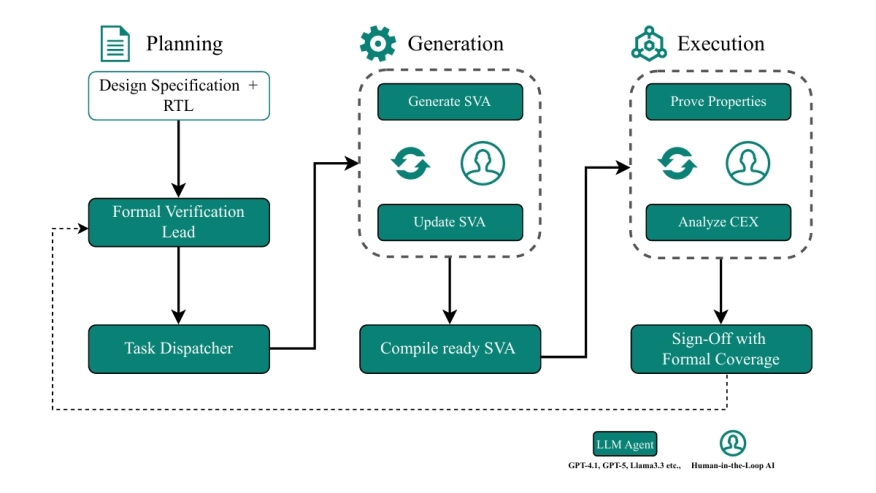

Coverage closure is a critical requirement in Integrated Chip (IC) development process and key metric for verification sign-off. However, traditional exhaustive approaches often fail to achieve full coverage within project timelines. This study presents an agentic AI-driven workflow that utilizes Large Language Model (LLM)-enabled Generative AI (GenAI) to automate coverage analysis for formal verification, identify coverage gaps, and generate the required formal properties. The framework accelerates verification efficiency by systematically addressing coverage holes. Benchmarking open-source and internal designs reveals a measurable increase in coverage metrics, with improvements correlated to the complexity of the design. Comparative analysis validates the effectiveness of this approach. These results highlight the potential of agentic AI-based techniques to improve formal verification productivity and support comprehensive coverage closure.

Coverage closure is a critical requirement in Integrated Chip (IC) development process and key metric for verification sign-off. However, traditional exhaustive approaches often fail to achieve full coverage within project timelines. This study presents an agentic AI-driven workflow that utilizes Large Language Model (LLM)-enabled Generative AI (GenAI) to automate coverage analysis for formal verification, identify coverage gaps, and generate the required formal properties. The framework accelerates verification efficiency by systematically addressing coverage holes. Benchmarking open-source and internal designs reveals a measurable increase in coverage metrics, with improvements correlated to the complexity of the design. Comparative analysis validates the effectiveness of this approach. These results highlight the potential of agentic AI-based techniques to improve formal verification productivity and support comprehensive coverage closure.

Index Terms — Agentic AI, LLM, Hardware Design, Formal Verification, Coverage

To read the full article, click here

Related Semiconductor IP

- Ultra Ethernet MAC & PCS 100G/200G/400G/800G

- Ethernet PCS 100G/200G/400G/800G/1.6T

- Ethernet MAC 100G/200G/400G/800G/1.6T

- Junction Over-Temperature Detector with Linear Centigrade-to-Voltage Output - X-FAB XT018

- Performance P570 Gen 3

Related Articles

- How formal verification saves time in digital IP design

- Don't over-constrain in formal property verification (FPV) flows

- Formal Verification Has It Covered!

- Formal property verification: A tale of two methods

Latest Articles

- Closer in the Gap: Towards Portable Performance on RISC-V Vector Processors

- TTP: A Hardware-Efficient Design for Precise Prefetching in Ray Tracing

- Heterogeneous SoC Integrating an Open-Source Recurrent SNN Accelerator for Neuromorphic Edge Computing on FPGA

- A Reconfigurable Multiplier Architecture for Error-Resilient Applications in RISC-V Core

- ObfAx: Obfuscation and IP Piracy Detection in Approximate Circuits