LUTstructions: Self-loading FPGA-based Reconfigurable Instructions

By Philippos Papaphilippou, University of Southampton

Abstract

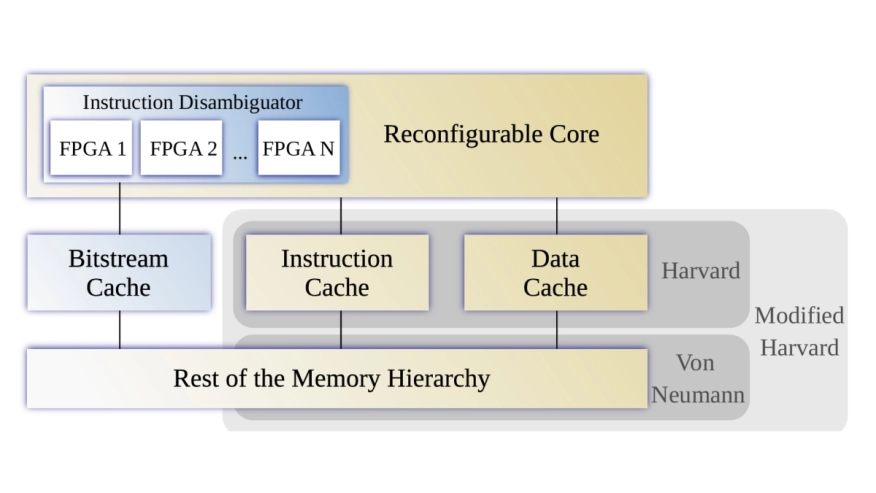

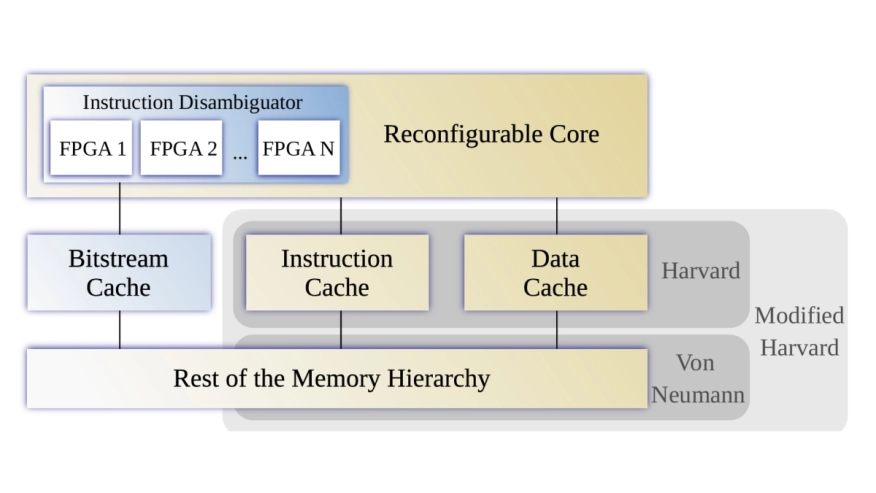

General-purpose processors feature a limited number of instructions based on an instruction set. They can be numerous, such as with vector extensions that include hundreds or thousands of instructions, but this comes at a cost; they are often unable to express arbitrary tasks efficiently. This paper explores the concept of having reconfigurable instructions by incorporating reconfigurable areas in a softcore. It follows a relatively-recently proposed computer architecture concept for seamlessly loading instruction implementation-carrying bitstreams from main memory. The resulting softcore is entirely evaluated on an FPGA, essentially having an FPGA-on-an-FPGA for the instruction implementations, with no notable operating frequency overhead. This is achieved with a custom FPGA architecture called LUTstruction, which is tailored towards low-latency for custom instructions and wide reconfiguration, as well as a soft implementation for the purposes of architectural exploration.

General-purpose processors feature a limited number of instructions based on an instruction set. They can be numerous, such as with vector extensions that include hundreds or thousands of instructions, but this comes at a cost; they are often unable to express arbitrary tasks efficiently. This paper explores the concept of having reconfigurable instructions by incorporating reconfigurable areas in a softcore. It follows a relatively-recently proposed computer architecture concept for seamlessly loading instruction implementation-carrying bitstreams from main memory. The resulting softcore is entirely evaluated on an FPGA, essentially having an FPGA-on-an-FPGA for the instruction implementations, with no notable operating frequency overhead. This is achieved with a custom FPGA architecture called LUTstruction, which is tailored towards low-latency for custom instructions and wide reconfiguration, as well as a soft implementation for the purposes of architectural exploration.

Keywords: FPGA, reconfigurable instructions, custom instruction, RISC-V, bit stream cache, soft instruction, eFPGA, virtual FPGA

To read the full article, click here

Related Semiconductor IP

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

- Vector-Capable Embedded RISC-V Processor

- Compact Embedded RISC-V Processor

Related Articles

- Reconfiguring Design -> Reconfigurable computing aims at signal processing

- Reconfigurable signal processing key in base station design

- High-Performance DSPs -> Reconfigurable coprocessors create flexibility in DSP apps

- High-Performance DSPs -> Reconfigurable approach supersedes VLIW/ superscalar

Latest Articles

- Closer in the Gap: Towards Portable Performance on RISC-V Vector Processors

- TTP: A Hardware-Efficient Design for Precise Prefetching in Ray Tracing

- Heterogeneous SoC Integrating an Open-Source Recurrent SNN Accelerator for Neuromorphic Edge Computing on FPGA

- A Reconfigurable Multiplier Architecture for Error-Resilient Applications in RISC-V Core

- ObfAx: Obfuscation and IP Piracy Detection in Approximate Circuits