Verification and Validation (V&V)-in-the-Loop for RISC-V Design: The Holistic Vision of BZL

By Sajjad Ahmed, Alexander Kropotov, Roberto Ignacio Genovese, Bernat Homs, Eloi Merino, Francesco Urbani, Henrique Yano, Iván Díaz, Joan Gracia Fernandez, Matteo Toselli, Muhammad Imran, Muhammad Abu Bakar, Umar Haider Iqbal, Nadeem Yaseen, Quswar Abid, Shaista Cheema, Samuel Sanchez, Daniel Garcia, Joan Cabré, Mostafa Elyasi, Fernando Ayats, Miquel Moreto, Teresa Cervero, Oscar Palomar, Behzad Salami

Barcelona Supercomputing Center (BSC)

Abstract

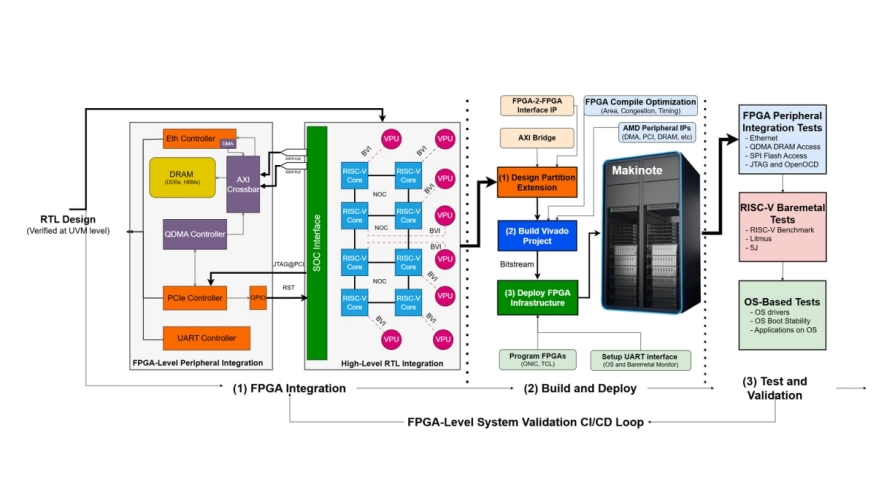

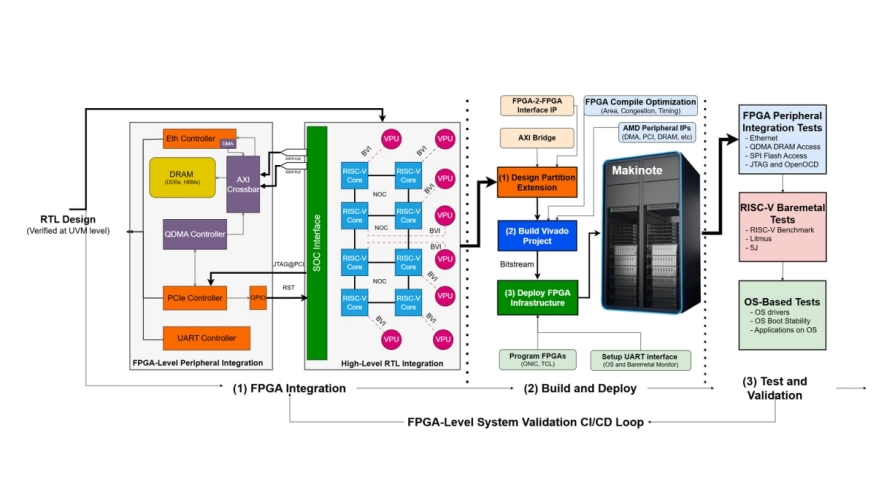

The Barcelona Zetascale Lab (BZL) project aims to strengthening Europe's capacity in the design and manufacture of RISC-V based high-performance computing chips. In this context, we present a holistic pre-silicon verification and validation (V&V) methodology targeting highly robust RISC-V chip designs. This paper provides an overview of BZL's V&V approach, which integrates three complementary platforms: (1) a UVM-based verification environment to thoroughly validate RTL functionality; (2) an FPGA-based validation platform that enables system-level pre-silicon hardware-software RTL validation; and (3) a CI/CD flow that continuously automates build, deployment, and tests across these domains. By embedding these platforms into an industrial-grade V&V loop and exploiting large-scale CPU and FPGA hardware infrastructures, the BZL project enables continuous evolution of reliable hardware development and software integration. We believe that the BZL's V&V flow represents a robust and scalable foundation for ensuring the pre-silicon functional correctness and system level validation of RISC-V chip designs, and can serve as a key enabler for strategic initiatives in Europe, such as EPI and DARE, and beyond.

The Barcelona Zetascale Lab (BZL) project aims to strengthening Europe's capacity in the design and manufacture of RISC-V based high-performance computing chips. In this context, we present a holistic pre-silicon verification and validation (V&V) methodology targeting highly robust RISC-V chip designs. This paper provides an overview of BZL's V&V approach, which integrates three complementary platforms: (1) a UVM-based verification environment to thoroughly validate RTL functionality; (2) an FPGA-based validation platform that enables system-level pre-silicon hardware-software RTL validation; and (3) a CI/CD flow that continuously automates build, deployment, and tests across these domains. By embedding these platforms into an industrial-grade V&V loop and exploiting large-scale CPU and FPGA hardware infrastructures, the BZL project enables continuous evolution of reliable hardware development and software integration. We believe that the BZL's V&V flow represents a robust and scalable foundation for ensuring the pre-silicon functional correctness and system level validation of RISC-V chip designs, and can serve as a key enabler for strategic initiatives in Europe, such as EPI and DARE, and beyond.

To read the full article, click here

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related Articles

- Design and implementation of a hardened cryptographic coprocessor for a RISC-V 128-bit core

- Importance of VLSI Design Verification and its Methodologies

- The Rise of RISC-V and ISO 26262 Compliance

- The Growing Imperative Of Hardware Security Assurance In IP And SoC Design

Latest Articles

- Verification and Validation (V&V)-in-the-Loop for RISC-V Design: The Holistic Vision of BZL

- EPAC: A RISC-V Accelerator from the European Processor Initiative

- AceleradorSNN: A Neuromorphic Cognitive System Integrating Spiking Neural Networks and Dynamic Image Signal Processing on FPGA

- VitaLLM: A Versatile and Tiny Accelerator for Mixed-Precision LLM Inference on Edge Devices

- SCENIC: Stream Computation-Enhanced SmartNIC