EPAC: A RISC-V Accelerator from the European Processor Initiative

By Filippo Mantovani 1, Fabio Banchelli 1, Pablo Vizcaino 1, Roger Ferrer 1, Oscar Palomar 1, Francesco Minervini 1, Jesus Labarta 1, Mauro Olivieri 1, Sebastiano Pomata 2, Pedro Marcuello 2, Jordi Cortina 2, Alberto Moreno 2, Josep Sans 2, Roger Espasa 2, Vassilis Papaefstathiou 3, Nikolaos Dimou 3, Georgios Ieronymakis 3, Antonis Psathakis 3, Michalis Giaourtas 3, Iasonas Mastorakis 3, Manolis Marazakis 3, Eric Guthmuller 4, Andrea Bocco 4, Jérôme Fereyre 4, César Fuguet 4, Mate Kovač 5, Mario Kovač 5, Luka Mrković 5, Josip Ramljak 5, Luca Bertaccini 6, Tim Fischer 6, Frank K. Gurkaynak 6, Paul Scheffler 6, Luca Benini 6, Bhavishya Goel 7, Madhavan Manivannan 7, Tiago Rocha 8, Nuno Neves 8, Jens Krüger 9,

1 Barcelona Supercomputing Center, Spain

2 Semidynamics, Spain

3 Foundation for Research and Technology– Hellas, Greece

4 Université Grenoble Alpes, CEA, LIST, France

5 University of Zagreb, Faculty of Electrical Engineering and Computing, Croatia

6 ETH Zürich, Switzerland

7 Chalmers University of Technology, Sweden

8 INESC-ID, Instituto Superior Técnico, Universidade de Lisboa Portuga

9 Fraunhofer ITWM, Germany

Abstract

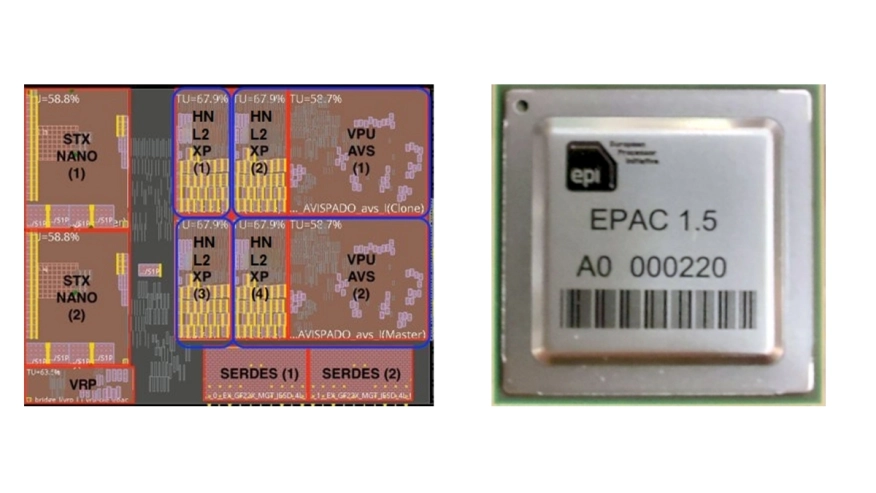

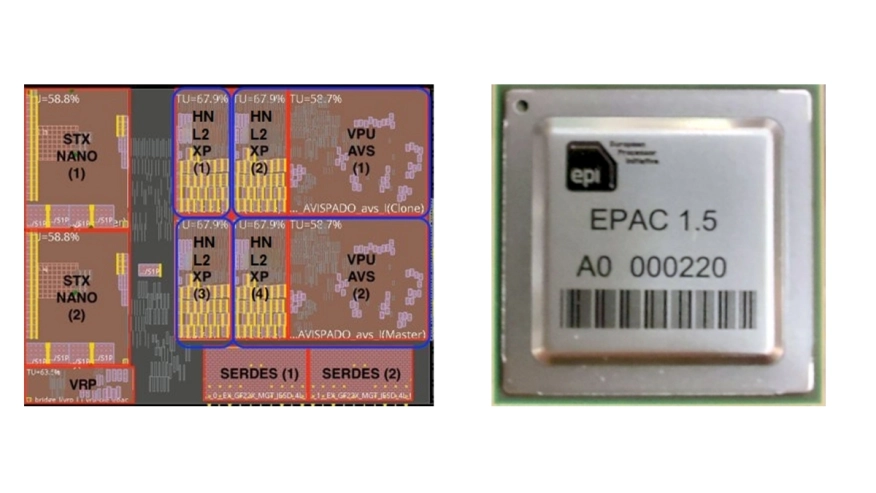

This paper presents EPAC, a RISC-V-based accelerator chip developed within the European Processor Initiative (EPI) as part of a multi-year, multi-partner effort to build a European HPC processor ecosystem. EPAC is implemented in GlobalFoundries 22FDX (GF22FDX) technology, covers an area of 27 sq mm with approximately 0.3 billion transistors, and integrates three distinct RISC-V compute tiles targeting different workload classes: VEC, a vector processing tile for double-precision HPC workloads; STX, a many-core tile optimized for stencil and machine learning computations; and VRP, a variable-precision tile for iterative numerical solvers requiring extended floating-point formats. All tiles are connected through a Coherent Hub Interface (CHI) based network-on-chip with a distributed L2 cache system and communicate with external memory via a SerDes link. The chip was taped out in GF22FDX technology and successfully brought up, with all major IP blocks validated. This paper describes the architecture of each tile and the uncore infrastructure, the integration and physical implementation process, and the board-level bring-up activities. It also reflects on the engineering and coordination lessons learned from a full chip design effort distributed across academic and industrial partners in Europe.

This paper presents EPAC, a RISC-V-based accelerator chip developed within the European Processor Initiative (EPI) as part of a multi-year, multi-partner effort to build a European HPC processor ecosystem. EPAC is implemented in GlobalFoundries 22FDX (GF22FDX) technology, covers an area of 27 sq mm with approximately 0.3 billion transistors, and integrates three distinct RISC-V compute tiles targeting different workload classes: VEC, a vector processing tile for double-precision HPC workloads; STX, a many-core tile optimized for stencil and machine learning computations; and VRP, a variable-precision tile for iterative numerical solvers requiring extended floating-point formats. All tiles are connected through a Coherent Hub Interface (CHI) based network-on-chip with a distributed L2 cache system and communicate with external memory via a SerDes link. The chip was taped out in GF22FDX technology and successfully brought up, with all major IP blocks validated. This paper describes the architecture of each tile and the uncore infrastructure, the integration and physical implementation process, and the board-level bring-up activities. It also reflects on the engineering and coordination lessons learned from a full chip design effort distributed across academic and industrial partners in Europe.

CCS Concepts

• Hardware →Integrated circuits; • Computer systems organization → Heterogeneous (hybrid) systems.

Keywords

RISC-V, European Processor Initiative, Vector Computing, Variable Precision, Stencil, Chip Tapeout, EPAC

To read the full article, click here

Related Semiconductor IP

- Configurable CPU tailored precisely to your needs

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- Multi-core capable 32-bit RISC-V CPU with vector extensions

- Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

- CPU IP Following the RVA23 Profile, supporting RVV1.0 and all extensions of Vector Crypto

Related Articles

- Creating a custom processor with RISC-V

- Maven Silicon's RISC-V Processor IP Verification Flow

- A formal-based approach for efficient RISC-V processor verification

- Soft Tiling RISC-V Processor Clusters Speed Design and Reduce Risk

Latest Articles

- EPAC: A RISC-V Accelerator from the European Processor Initiative

- AceleradorSNN: A Neuromorphic Cognitive System Integrating Spiking Neural Networks and Dynamic Image Signal Processing on FPGA

- VitaLLM: A Versatile and Tiny Accelerator for Mixed-Precision LLM Inference on Edge Devices

- SCENIC: Stream Computation-Enhanced SmartNIC

- Agentic AI-based Coverage Closure for Formal Verification