Verification Sanity in Chiplets & Edge AI: Avoid the “Second Design” Trap

As we gather at IP-SoC 2026, the industry consensus is clear: the monolithic SoC is no longer the only game in town. With the rise of chiplet-based architecture and Edge Generative AI, we are integrating more “black boxes” than ever. In this hyper-modular world, the “Second Design” problem isn’t just a nuisance. It’s a tape-out killer.

As we gather at IP-SoC 2026, the industry consensus is clear: the monolithic SoC is no longer the only game in town. With the rise of chiplet-based architecture and Edge Generative AI, we are integrating more “black boxes” than ever. In this hyper-modular world, the “Second Design” problem isn’t just a nuisance. It’s a tape-out killer.

For embedded FPGA (eFPGA), the stakes are higher than ever. To be viable in 2026, eFPGA IP must act like a trusted socket, not a science project.

The “Second Design” Problem in 2026

The fastest way to derail eFPGA adoption is to position it as a subsystem that must be verified twice: once as part of the SoC/Chiplet fabric and again as an independent programmable subsystem.

Verification teams are already stretched thin. Between hardware-software co-verification for AI stacks and the rising threshold of security verification, teams have no bandwidth for redundant tasks. If the eFPGA IP is treated like soft RTL, requiring full re-validation of internal timing and structural integrity, it becomes a liability.

The 2026 Reality

If the verification boundary is unclear, the regression space explodes. In an era where a 2nm re-spin can cost more than $20M, “flexible” soft fabrics look like “unbounded” risk.

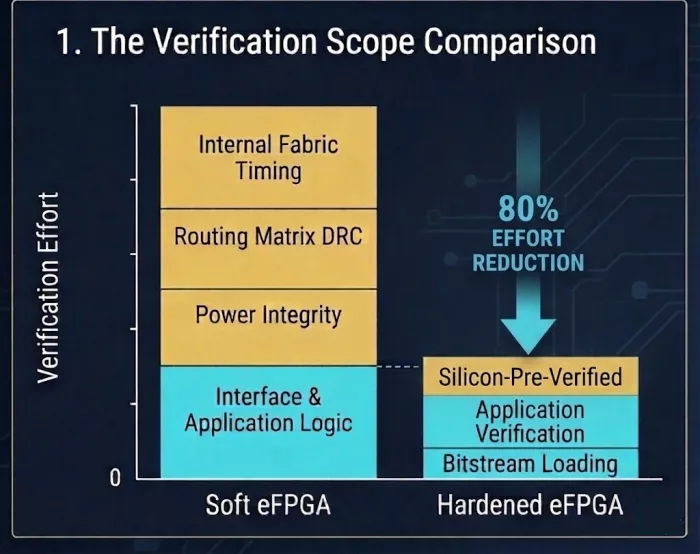

Hardened eFPGA: The Separation of Concerns

The solution is the same approach used for CPUs, SerDes, and HBM3: Separation of Concerns.

Hardened eFPGA IP enforces this separation by delivering a pre-verified GDSII macro. This mirrors how we handle the most complex IPs today:

- CPUs: No SoC team re-verifies out-of-order execution logic; they verify the AXI/CHI interfaces.

- Chiplets: You verify the Die-to-Die (D2D) interface, not the internal routing of the neighbor chiplet.

Hardened eFPGA follows this “Trusted Block” model. The IP provider guarantees the fabric; the SoC team verifies the integration. No more, no less.

Why Soft eFPGA Fails the 2026 Scalability Test

Soft eFPGA fabrics—delivered as synthesizable RTL—blur the lines that modern verification architects are trying to draw. By making the fabric part of the SoC’s logical design, you introduce:

1. Regression Creep: Changes in synthesis tools or PDK updates can alter fabric behavior, forcing a total re-validation.

2. AI-Assisted Verification Gaps: Modern AI-driven verification tools work best on stable, bounded IPs. A soft fabric creates a “moving target” that degrades the efficiency of LLM-based testbench generation.

3. Security Fragility: With the 2026 focus on Data Isolation, verifying a soft fabric against side-channel attacks becomes an order of magnitude harder than verifying a hardened, characterized macro.

What Verification Leads Actually Want

The sentiment at IP-SoC 2026 is clear: Verification teams are not looking for more features; they are looking for more certainty. As SoC complexity scales, the goal is to shrink the “untrusted” surface area of the design. The common refrain from lead architects is simple: “Don’t give me more logic to verify. Give me a clean contract.”

Hardened eFPGA delivers this contract by establishing a definitive boundary of responsibility:

- The Vendor’s Responsibility: Delivers a timing-closed, silicon-characterized macro. This includes pre-verified simulation models and hardware emulation targets that are guaranteed to represent the final silicon accurately.

- The SoC Team’s Responsibility: Focuses entirely on system-level integration. This includes interface compliance (e.g., ensuring the AXI interconnect is robust), bitstream security, and the functional correctness of the application logic mapped onto the fabric.

By removing the fabric itself from the SoC-level verification task, the “Second Design” problem disappears. The fabric becomes a reliable infrastructure—much like a standard library cell or a memory macro—allowing the team to focus their compute resources and engineering hours on their own unique IP.

Explore eFPGA IP:

Practical Flow for 2026

In practice, this allows teams to use Hardware-in-the-Loop (HIL) and Emulation to run actual AI workloads on the eFPGA logic before silicon, without ever worrying if the underlying fabric will fail a timing check.

The Bottom Line

In 2026, we don’t have time for “Second Designs.” The success of eFPGA hinges on it being operationally invisible to the verification flow.

By keeping the fabric fixed and trusted, hardened eFPGA aligns with the way modern, high-volume silicon is built. It moves eFPGA from a “special case” to a standard socket in the heterogeneous compute era.

Are you at IP-SoC 2026?

QuickLogic is exhibiting at D&R IP SoC Days. Stop by to see how eFPGA Hard IP brings flexibility and predictability to SoC design. 📍 Booth #21

Also join us at 5:00 PM for:

“Future-Proofing SoCs: eFPGA IP Use Cases and Integration Made Predictable” Presented by Trey Peterson, Field Application Engineer

As SoCs evolve, designing for the unknown is becoming the norm. In this session, we’ll cover how eFPGA enables:

- Flexible data processing and pre-processing

- I/O adaptability across changing interfaces

- Programmable security and hardware updates

- Predictable integration with Hard eFPGA IP

Related Semiconductor IP

- eFPGA Hard IP Generator

- Radiation-Hardened eFPGA

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- eFPGA on GlobalFoundries GF12LP

Related Blogs

- Tape-out Risk in the Age of Edge AI: The Case for GPU IP

- Analog Design and Layout Migration automation in the AI era

- Physical AI at the Edge: A New Chapter in Device Intelligence

- Arm in the agentic era: Scaling the converged AI data center

Latest Blogs

- Enabling Memory Choice for Modern AI Systems: Tenstorrent and Rambus Deliver Flexible, Power-Efficient Solutions

- Verification Sanity in Chiplets & Edge AI: Avoid the “Second Design” Trap

- Embedded Security explained: Cryptographic Hash Functions

- Arm and Google Cloud redefine agentic AI infrastructure with Axion processors

- A Bench-to-In-Field Telemetry Platform for Datacenter Power Management