Vendor:

PRSsemicon Group

Category:

USB

Certified USB 5G & 10G, USB2 Hub controller

USB 5G, 10G and 2.0 Hub controller is a configurable core and implements the USB Hub functionality that can be interfaced with th…

Overview

USB 5G, 10G and 2.0 Hub controller is a highly configurable core and implements the USB Hub functionality that can be interfaced with third party USB PHY’s. The Hub Controller core can be configured to support upto 15 downstream ports.

The Hub Controller core supports all defined USB power states. The design is carefully partitioned to support standard power management schemes. Optionally, it can be configured to manage power mode transitions of the controller and the USB PHY for aggressive power savings required for bus powered hubs.

The controller's simple, configurable and layered architecture is independent of application logic, PHY designs, implementation tools and, most importantly, the target technology. Our solution allows the licensees to easily migrate among FPGA, Gate array and Standard cell technologies optimally. Its flexible backend interface makes it easy to be integrated into wide range of applications

The Hub Controller core supports all defined USB power states. The design is carefully partitioned to support standard power management schemes. Optionally, it can be configured to manage power mode transitions of the controller and the USB PHY for aggressive power savings required for bus powered hubs.

The controller's simple, configurable and layered architecture is independent of application logic, PHY designs, implementation tools and, most importantly, the target technology. Our solution allows the licensees to easily migrate among FPGA, Gate array and Standard cell technologies optimally. Its flexible backend interface makes it easy to be integrated into wide range of applications

Key features

- Compliant with USB2.0, 5G, 10G Specifications

- Configurable number of downstream ports

- Configurable Core Frequency

- Configurable Internal datapath width: 32, 64, or 128 bits

- Compliant with standard USB 3.0 PHY Interface

- Configurable PHY Interface width: 8, 16, or 32 bits

- Efficient buffering scheme for forwarding packets through hub with minimal latency

- Supports Bus and Self Powered Hub implementations

- USB 3.0 low power states support

- Extensive clock tree gating and multiple power well support for aggressive power savings

- Support for various Hardware and Software Configurability regarding Core characteristics

- Register Interface for internal Register Access

- Optional support for Compound Device Support

- Optional Support for USB2.0 Hub controller

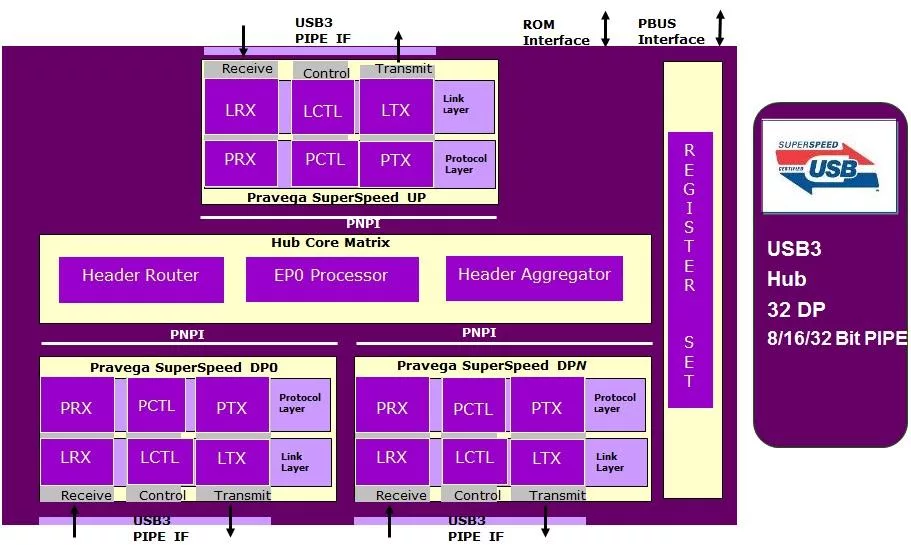

Block Diagram

usb_hub block diagram

What’s Included?

- Synthesizable Verilog RTL

- Configurable System Verilog Verification IP.

- Synthesis Scripts

- Documentation

Specifications

Identity

Part Number

usb_hub

Vendor

PRSsemicon Group

Type

Silicon IP

Provider

PRSsemicon Group

HQ:

India

PRSsemicon is a fabless semiconductor company with a vision to provide Professional Reliable Solutions, Services & Support to our customers & partners globally.

Our R&D Business Unit develops cutting edge IP Products, Our Business administration BU ties up with several partners who require our support to promote & resell their reliable IP's, Our Services BU helps customer on ASIC/FPGA/SoC Design Verification & Validation services.

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

In addition to performance and interoperability, achieving low power has been one of the requirements for industry standards specifications. Some of the key specifications like Universal Serial Bus (USB), PCI Express (PCIe), and MIPI have defined power saving features for burst traffic. This whitepaper explains how Synopsys USB IP offers low power using various low power states that go beyond the basic features.

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

Gervais Fong, Synopsys

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Sharmion Kerley, MIPI Alliance

Frequently asked questions about USB IP cores

What is Certified USB 5G & 10G, USB2 Hub controller?

Certified USB 5G & 10G, USB2 Hub controller is a USB IP core from PRSsemicon Group listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.