SDI II Intel® FPGA IP Core

The serial digital interface (SDI) II Intel FPGA intellectual property (IP) core implements a transmitter, receiver or full-duple…

Overview

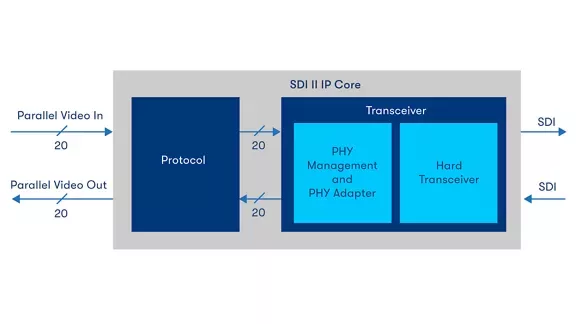

The serial digital interface (SDI) II Intel FPGA intellectual property (IP) core implements a transmitter, receiver or full-duplex SDI at standard definition, high definition or 3G to 12G rate as defined by the Society of Motion Picture and Television Engineers. The SDI II IP core supports multiple standards. These modes provide automatic receiver rate detection and transceiver dynamic reconfiguration.

|

IP Core Feature |

Description |

|---|---|

|

Transceiver data interface |

20 bit, 40 bit, and 80 bit |

|

Supported SDI standards and video formats |

Note: Not all devices support all formats, see “Device Support” below |

|

SMPTE support |

|

|

Other features |

|

Block Diagram

What’s Included?

- Design file (encrypted source code or post-synthesis netlist)

- Simulation model for ModelSim*- Intel® FPGA Edition

- Timing and/or layout constraints

- Testbench or design example

- Documentation with revision control

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is SDI II Intel® FPGA IP Core?

SDI II Intel® FPGA IP Core is a Video Transport IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.