SMPTE Serial Data Interface (SDI) Synthesizable Transactor

SMPTE SDI Synthesizable Transactor provides an smart way to verify the SMPTE SDI component of a SOC or a ASIC in Emulator or FPGA…

Overview

SMPTE SDI Synthesizable Transactor provides an smart way to verify the SMPTE SDI component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's SMPTE SDI Synthesizable Transactor is fully compliant with standard SMPTE SDI Specification and provides the following features.

Key features

- Supports SMPTE ST 425-1:2011 (Source Image Format and Ancillary Data Mapping for the 3 Gb/s Serial Interface)

- Supports SMPTE ST 292-1:2011 (1.5 Gb/s Signal/Data Serial Interface)

- Supports SMPTE ST 372:2011 (Dual Link 1.5 Gb/s Digital Interface for 1920 × 1080 and 2048 × 1080 Picture Formats)

- Supports SMPTE 296M-2001 (1280x720 Progressive Image Sample Structure Analog and Digital Representation and Analog Interface)

- Supports SMPTE 274M-2008 (1920 x 1080 Image Sample Structure, Digital Representation and Digital Timing Reference Sequences for Multiple Picture Rates)

- Supports SMPTE 428-9-2008 (D-Cinema Distribution Master - Image Pixel Structure Level 3 - Serial Digital Interface Signal Formatting)

- Supports SMPTE ST 2048-2:2011 (2048x1080 Digital Cinematography Production Image FS/709 Formatting for Serial Digital Interface)

- Supports SMPTE ST 291:2010 (Ancillary Data Packet and Space Formatting)

- Supports Dual standard support for 270-Mbps and 1.5-Gbps SDI

- Supports full SMPTE SDI Tx and Rx device functionality

- Supports Serialization and de-serialization

- Supports NRZI encoding

- Protocol supports below video format mapping structures

- 4:2:2 (Y’C’BC’R)/10-bit

- 4:4:4 (R’G’B’)/10-bit

- 4:4:4:4 (R’G’B’ +A)/10-bit

- 4:4:4 (Y’C’BC’R)/10-bit

- 4:4:4:4 (Y’C’BC’R+A)/10-bit

- 4:4:4 (R’G’B’)/10-bit

- 4:4:4:4 (R’G’B’ +A)/10-bit

- 4:4:4 (Y’C’BC’R)/10-bit

- 4:4:4:4 (Y’C’BC’R+A)/10-bit

- 4:4:4 (R’G’B’)/12-bit

- 4:4:4 (Y’C’BC’R)/12-bit

- 4:4:4 (X’Y’Z’)/12-bit

- 4:2:2 (Y’C’BC’R)/12-bit

- Supports Dual-link channel interface

- Supports 24-bit Digital Audio data

- Supports 4 to 32 Audio channels

- Supports SMPTE ST 299-1:2009 (24-Bit Digital Audio Format for SMPTE 292 Bit-Serial Interface)

- Supports SMPTE ST 299-2:2010 (Extension of the 24-Bit Digital Audio Format to 32 Channels for 3 Gb/s Bit-Serial Interfaces)

- Supports Audio extended data packets

- Supports scrambler which can be enabled or disabled

- Supports insertion of scrambler errors

- Supports error correction code (ECC)

- Supports detections and reporting the following errors

- Invalid EAV code

- Invalid SAV code

- Invalid CRC error

- Invalid LN error

- Invalid parity error

- Invalid NRZI encoding error

- Invalid 10bit code

- ECC errors

- Invalid ADF errors

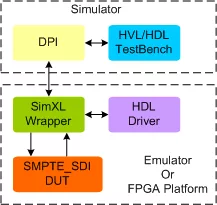

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the SMPTE SDI testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is SMPTE Serial Data Interface (SDI) Synthesizable Transactor?

SMPTE Serial Data Interface (SDI) Synthesizable Transactor is a Video Transport IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.