SMPTE Serial Data Interface (SDI) Verification IP

SMPTE SDI Verification IP is fully compliant with SMPTE SDI Specification.

Overview

SMPTE SDI Verification IP is fully compliant with SMPTE SDI Specification. It includes an extensive test suite covering most of the possible scenarios. It performs all possible protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively.

SMPTE Serial Data Interface (SDI) Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SMPTE Serial Data Interface (SDI) Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full SMPTE SDI Tx and Rx device functionality.

- Supports 12 Gb/s Signal/Data Serial Interface as per SMPTE ST 2082-1:2015.

- Supports 6 Gb/s Signal/Data Serial Interface as per SMPTE ST 2081-1-2015.

- Supports Source Image Format and Ancillary Data Mapping for the 3 Gb/s Serial Interface as per SMPTE ST 425-1:2011

- Supports 1.5 Gb/s Signal/Data Serial Interface as per SMPTE ST 292-1:2011

- Supports Dual Link 1.5 Gb/s Digital Interface for 1920 × 1080 and 2048 × 1080 Picture Formats as per SMPTE ST 372:2011

- Supports 1280x720 Progressive Image Sample Structure Analog and Digital Representation and Analog Interface as per SMPTE 296M-2001

- Supports 1920 x 1080 Image Sample Structure, Digital Representation and Digital Timing Reference Sequences for Multiple Picture Rates as per SMPTE 274M-2008

- Supports D-Cinema Distribution Master - Image Pixel Structure Level 3 - Serial Digital Interface Signal Formatting as per SMPTE 428-9-2008

- Supports 2048x1080 Digital Cinematography Production Image FS/709 Formatting for Serial Digital Interface as per SMPTE ST 2048-2:2011

- Supports 2048 × 1080 and 4096 × 2160 Digital Cinematography Production Image Formats FS/709 as per SMPTE ST 2048-1:2011

- Supports Ultra High Definition Television —Image Parameter Values for Program Production as per SMPTE ST 2036-1:2014

- Supports Ancillary Data Packet and Space Formatting as per SMPTE ST 291:2010

- Supports Dual standard support for 270-Mbps and 1.5-Gbps SDI.

- Supports 10-bit/20-bit/40-bit parallel interfaces.

- Supports Serialization and de-serialization.

- Supports NRZI channel encoding.

- Supports below video format mapping structures

- 4:2:2 (Y’C’BC’R)/10-bit

- 4:4:4 (R’G’B’)/10-bit

- 4:4:4:4 (R’G’B’ +A)/10-bit

- 4:4:4 (Y’C’BC’R)/10-bit

- 4:4:4:4 (Y’C’BC’R+A)/10-bit

- 4:4:4 (R’G’B’)/10-bit

- 4:4:4:4 (R’G’B’ +A)/10-bit

- 4:4:4 (Y’C’BC’R)/10-bit

- 4:4:4:4 (Y’C’BC’R+A)/10-bit

- 4:2:0 (Y’C’BC’R)/10-bit

- 4:4:4 (R’G’B’)/12-bit

- 4:4:4 (Y’C’BC’R)/12-bit

- 4:4:4 (X’Y’Z’)/12-bit

- 4:2:2 (Y’C’BC’R)/12-bit

- 4:2:0 (Y’C’BC’R)/12-bit

- Supports up to Quad-link channel interface.

- Supports 16-bit/20-bit/24-bit Digital Audio data.

- Supports 4 to 32 Audio channels.

- Supports 24-Bit Digital Audio Format for SMPTE 292 Bit-Serial Interface as per SMPTE ST 299-1:2009

- Supports Extension of the 24-Bit Digital Audio Format to 32 Channels for 3 Gb/s Bit-Serial Interfaces as per SMPTE ST 299-2:2010

- Supports Audio extended data packets.

- Supports for Scrambler.

- Supports dynamic speed switch between SD, HD, 3G, 6G and 12G in parallel interface.

- Supports insertion of scrambler errors.

- Supports error correction code (ECC).

- Detects and reports the following errors.

- Invalid EAV code

- Invalid SAV code

- Invalid CRC error

- Invalid LN error

- Invalid parity error

- Invalid NRZI encoding error

- Invalid 10bit code

- ECC errors

- Invalid ADF errors

- SMPTE SDI Verification IP comes with complete testsuite to test every feature of SMPTE SDI specification.

- Monitors, detects and notifies the test bench of significant events such as transactions, warnings, timings and protocol violations.

- Status counters for various events on bus.

- Supports callbacks in monitor, device and sensor BFMs for user processing of data.

- Functional coverage for complete SMPTE SDI features

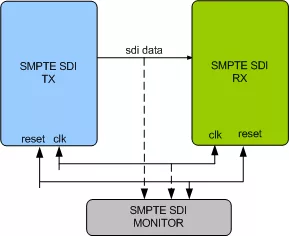

Block Diagram

Benefits

- Faster testbench development and more complete verification of SMPTE_SDI designs.

- Easy to use command interface simplifies testbench control and configuration of receiver and transmitter.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SMPTE_SDI testcases.

- Examples showing how to connect various components, and usage of Transmitter, Receiver and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is SMPTE Serial Data Interface (SDI) Verification IP?

SMPTE Serial Data Interface (SDI) Verification IP is a Video Transport IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.