ARINC 818 Verification IP

ARINC 818 Verification IP implements the Digital Video Interface standards for all types of flight deck video.

Overview

ARINC 818 Verification IP implements the Digital Video Interface standards for all types of flight deck video. ARINC 818 Verification IP provides an smart way to verify the ARINC 818 standard video data transmission and control interfaces between transmitter and receiver. The SmartDV's ARINC 818 Verification IP is fully compliant with ARINC specification 818-2 and provides the following features.

ARINC 818 Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

ARINC 818 Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full ARINC 818 source device and sink device functionality.

- Supports ARINC specification 818 - 2.

- Supports serial & parallel bit ordering.

- Supports following bit rates

- 1.0625 Gbps

- 1.5 Gbps

- 1.62 Gbps

- 2.125 Gbps

- 2.5 Gbps

- 3.1875 Gbps

- 4.25 Gbps

- 5.0 Gbps

- 6.375 Gbps

- 8.5 Gbps

- 12.75 Gbps

- 14.025 Gbps

- 21.0375 Gbps

- 28.05 Gbps

- Supports following encoding

- 8B/10B encoding

- 64B/66B encoding

- Supports following pixel formats

- Monochrome

- RGB (Red, Green, Blue)

- RGGB (Red, Green, Green, Blue)

- RGBA (Red, Green, Blue, Alpha)

- YlQ

- YCbCr (4:2:2)

- Color Palette, Auxiliary Object table

- Color Palette, External table

- Color Palette, Internal table

- Packed RGB

- Packed RGGB

- Packed RGBA

- Packed YlQ

- Packed YCbCr (4:2:2)

- Supports following Aspect ratio

- 1:1

- 1:1.2

- 1.2:1

- NTSC (approx 8:9)

- PAL (16:15)

- Supports following Pixel Array Order

- Left to Right, Top to Bottom

- Right to Left, Top to Bottom

- Left to Right, Bottom to Top

- Right to Left, Bottom to Top

- Top to Bottom, Left to Right

- Top to Bottom, Right to Left

- Bottom to Top, Left to Right

- Bottom to Top, Right to Left

- Supports following packing format

- 8-bit components, four components per transmission word

- 10-bit components, three components per transmission word

- 12-bit components, two and 2/3 components per transmission word

- 16-bit components, two components per transmission word

- 20-bit components, one and 12/20 components per transmission word

- 24-bit components, one and 1/3 components per transmission word

- 32-bit components, one component per transmission word

- Supports Interlaced and Non-Interlaced scan type

- Supports 32-bit full image CRC

- The model has a rich set of configuration parameters to control ARINC 818 functionality.

- Supports Ancillary, Audio and Video data transmission as per ARINC 818 standard

- Detects and reports the following errors,

- Invalid frame fields

- Invalid EOF and SOF

- Oversize and undersize frames

- Disparity errors

- Invalid code group errors

- Invalid control character

- Invalid data character

- Sync errors

- Invalid packing injection and detection

- CRC errors

- Status counters for various events on bus.

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Supports constraints Randomization.

- Callbacks in transmitter,receiver and monitor for various events.

- Functional coverage for complete ARINC 818 features.

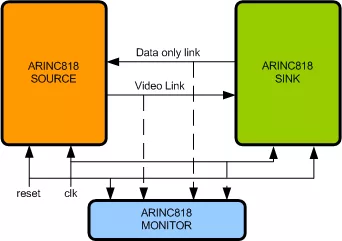

Block Diagram

Benefits

- Faster testbench development and more complete verification of ARINC 818 designs.

- Easy to use command interface simplifies testbench control and configuration of Transmitter,Receiver and Monitor

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the ARINC 818 testcases.

- Examples showing how to connect various components, and usage of Transmitter,Receiver and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is ARINC 818 Verification IP?

ARINC 818 Verification IP is a Video Transport IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.