PHY for PCIe 5.0 and CXL

The PHY IP for PCI Express® (PCIe®) 5.0 is a high-performance SerDes configurable to operate from 1.25Gbps to 32Gbps in NRZ mode.

Overview

The PHY IP for PCI Express® (PCIe®) 5.0 is a high-performance SerDes configurable to operate from 1.25Gbps to 32Gbps in NRZ mode. This state-of-the-art PHY is designed specifically for infrastructure and data center applications. The SerDes’s ultra-long-reach equalization and robust clock-data recovery capabilities allow it to achieve unparalleled performance and reliability. In addition, the SerDes IP features low data path latency and low power consumption, making it ideal for deployment in time-sensitive applications in high-performance computing (HPC), artificial intelligence and machine learning (AI/ML), networking, and storage systems.

Key features

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Advanced equalization and clock-data-recovery to deliver unmatched channel loss handling performance and reliability

- Eye Surf —provides convenient access to an integrated non-destructive real-time eye scope and BER bathtub curve to monitor the bit error rate (BER) and the link performance during live traffic

- Comprehensive set of diagnostic and test features is embedded and easily accessible by the user to accelerate silicon bring-up and simplify troubleshooting

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports PIPE 5.2 standard

- Built-in support for 1x16 to 16x1 modes of operation

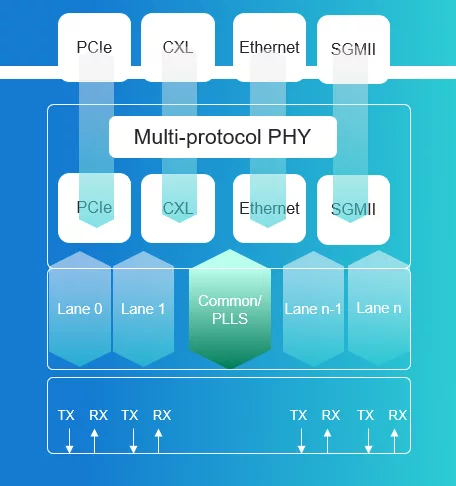

Block Diagram

Applications

- Communications,

- Consumer Electronics,

- Data Processing,

- Industrial and Medical,

- Military/Civil Aerospace

What’s Included?

- Integration Views: Verilog behavioral model, GDSII, CDL, and power models

- Synthesizable RTL

- DFT-Verilog netlists with SS/FF, CTL, and BSDL

- Reference Verilog testbenches used for generating SoC-level VCD ATE test patterns for PHY

- IBIS-AMI kit

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 5nm | N5 | Silicon Proven |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is PHY for PCIe 5.0 and CXL?

PHY for PCIe 5.0 and CXL is a Multi-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.