16Gbps SerDes IP on TSMC 12nm

As the demand for higher data rates and increased serial I/O density intensifies, the performance requirements for next-generatio…

Overview

As the demand for higher data rates and increased serial I/O density intensifies, the performance requirements for next-generation SerDes designs become more stringent, particularly in managing area and power constraints. Multi-Gigabit/s serial transceivers are rapidly supplanted traditional parallel interfaces across numerous applications. High-speed transceivers must seamlessly support a range of data rates to accommodate new link speeds and emerging standards, all while maintaining backward compatibility with legacy systems. At elevated data rates, each component must meet rigorous performance specifications to ensure overall link integrity, especially in managing jitter and maintaining a strict bit error rate amidst challenging interconnect conditions such as channel loss, impedance discontinuities caused by packaging and connectors, and crosstalk from routing limitations in the package and motherboard.

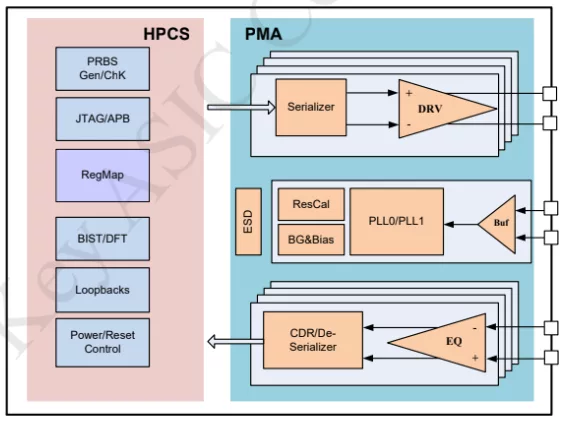

To effectively meet these challenges, serial I/O design has advanced, incorporating increasingly sophisticated architectures and cutting-edge techniques. Key ASIC’s multi-mode transceiver IP, which integrates both the PMA and PCS layers, is specifically engineered for applications demanding low power consumption and high performance. It is highly configurable and can be efficiently integrated with user logic or SoC resources, supporting data rates ranging from 1Gbps to 16Gbps.

Key features

- Data rate: 1–16Gbps per lane

- Supports PCIe, SATA, USB3.1, JESD204C, XAUI, SRIO, and more

- TX: 3-tap FFE, de-emphasis control

- RX: CTLE, multi-tap DFE

- Adaptive equalization, SSC, PRBS generator/checker

- On-chip eye monitor & BIST features

- 2x QPLL for flexible clocking

- JTAG & APB accessible register map

Block Diagram

Benefits

- High-speed serial connectivity in compact area

- Silicon-proven reliability

- Multi-standard support for versatile applications

- Integrated debug and monitoring functions reduce development time

What’s Included?

- Datasheet & integration guide

- Encrypted RTL or hard macro

- Layout views (.LEF/.GDS)

- Timing & power reports

- Register map, eye diagram spec

- Verification testbenches

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC | Silicon Proven |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 16Gbps SerDes IP on TSMC 12nm?

16Gbps SerDes IP on TSMC 12nm is a Multi-Protocol PHY IP core from Key ASIC listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.