SerDes IP

your custom Switch Fabric, AI, or HPC ASIC with Credo’s SerDes IP.

Overview

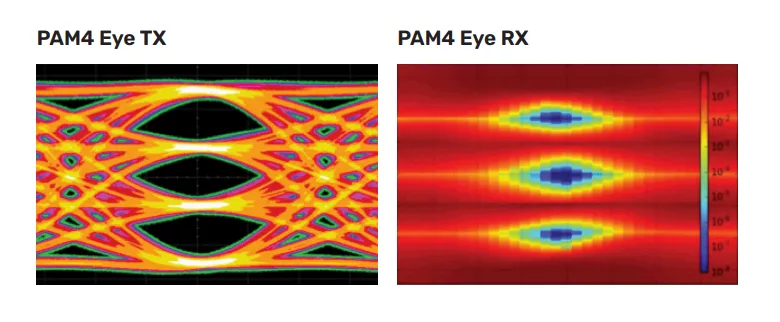

Complete your custom Switch Fabric, AI, or HPC ASIC with Credo’s advanced SerDes IP. Our proven, innovative architecture is designed in TSMC’s 28nm, 16/12nm, N7/N6, N5/N4 and N3 processes. Whether you’re moving from 28G to 56G or 112G, we have SerDes IP for you. Credo designs SerDes IP that delivers industry-leading performance and power, but are manufactured in lower risk, lower cost mature processes.

Credo designs SerDes IP that optimally balances performance, power and manufacturing process costs and risks. Our unique, patented mixed signal architecture is the foundation for our high performance and low power SerDes technology. The architectural approach taken by Credo has enabled us to design in mature fabrication processes yet deliver leading-edge performance and power. Credo was the first to deliver 56G NRZ in 40nm, 56G PAM4 in 28nm and 112G PAM4 in 28nm.

By contrast, other industry solutions have moved to power-hungry designs in the most advanced silicon processing geometries for performance, yet struggle to meet the fundamental power requirements.

SerDes IP Availability

Our IP is designed for a variety of TSMC fabrication processes.

| TSMC 28nm | TSMC 16nm/12nm | TSMC 7nm | |

| 28G NRZ | MR, LR | MR, LR | MR, LR |

| 56G PAM4 | VSR, MR, LR | VSR, MR, LR | |

| 112G PAM4 | XSR, VSR, MR, LR | XSR, VSR, MR, LR |

Key features

- Integrated PLL

- Robust clock distribution architecture

- Advanced mixed signal analog or DSP equalization architectures

- Fully adaptive and programmable RX equalization

- Auto-negotiation

- Link Training

- Excellent random jitter performance

- Robust clock data recovery

- Complete diagnostic suite

- On-chip PRBS generation and checking

- RX monitors

- Loop back testing

- JTAG/IEEE 1500

- MCU per lane

- Parameters

- 28G NRZ MR, LR in 28nm, 16/12nm, N7/N6, N5/N4 and N3 processes

- 56G PAM4 XSR, VSR, MR, LR in 16/12nm, N7/N6, N5/N4 and N3 processes

- 112G PAM4 XSR, VSR, MR, LR in 16/12nm, N7/N6, N5/N4 and N3 processes

- From a few dB to 35dB bump-to-bump insertion loss

Block Diagram

Benefits

- Benefits : Low Power

- Excellent insertion loss handling for enterprise class backplane and optical applications.

- High-performance supply noise immunity for SoC integration.

- Build-in Analog calibration for handling process variation.

Applications

- High speed wireline communication for HPC and AI SoCs

What’s Included?

- Verilog Model

- LEF view

- Timing Libraries

- ATPG Model & Netlist

- GDS

- Spice Netlist

- Usage Guide and Documentation Free Integration Review

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC | Silicon Proven |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is SerDes IP?

SerDes IP is a Multi-Protocol PHY IP core from Credo Semiconductor listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.