CNN AI IP Core

DeepMentor has developed an AI IP that combines low-power and high-performance features with the RISC-V SOC.

Overview

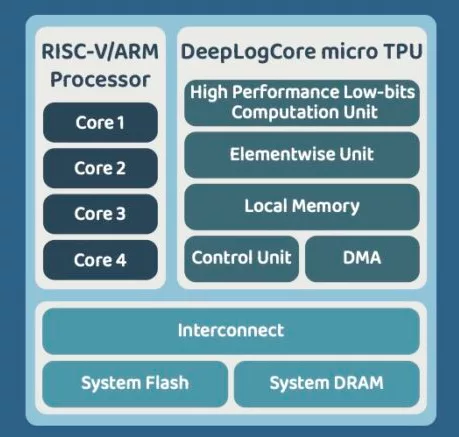

DeepMentor has developed an AI IP that combines low-power and high-performance features with the RISC-V SOC. This integration allows customers to quickly create unique AI SOC without worrying about software integration or system development issues. DeepLogCore supports both RISC-V and ARM systems, enabling faster and more flexible development.

DeepLogcore is a soft AI IP compatible with a wide range of processes, particularly mature and power-saving low-cost processes between 28nm to 130nm. As a result, customers can control their manufacturing costs according to their specific needs and market demands.

Key features

- High-efficiency Al Silicon Intellectual Property

- The performance of Al silicon can reach @SO 0Mhz 1 TOP/s.

- Supports DeepMentor Exclusive Low-distortion MAT Training Models

- In the case of Int4, the accuracy is only reduced by 1-2%. (Example: yolov4 - 416x416, coco, etc.)

- High Integrity of Software and Hardware

- DeepLogCore service includes the operating system, the silicon intellectual property driver, and the establishment and deployment of Al models. Clients don't need to bother to research and integrate silicon intellectual property.

- Complete Maintenance and Retraining Systems

- Products can be updated at any time by using the maintenance and retraining services on our DeepLogMaker platform.

Block Diagram

Benefits

- power-saving low-cost processes (28nm~130nm)

- Development time 30~100x faster than manual Verilog coding

- Flexible to update the latest AI features

- Supports DeepMentor Exclusive Low-distortion Training Models

Applications

- Object classification

- Object detection

- Face detection/identification

- Human pose detection

- Hand-gesture recognition

- Eye tracking

- Image segmentation

- Image beautification

- Super resolution

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Edge AI Accelerator IP core

Using edge AI processors to boost embedded AI performance

The Industry’s First USB4 Device IP Certification Will Speed Innovation and Edge AI Enablement

Accelerating Your Development: Simplify SoC I/O with a Single Multi-Protocol SerDes IP

IoT Was Interesting, But Follow the Money to AI Chips

Designing Energy-Efficient AI Accelerators for Data Centers and the Intelligent Edge

Frequently asked questions about Edge AI Accelerator IP cores

What is CNN AI IP Core?

CNN AI IP Core is a Edge AI Accelerator IP core from DeepMentor listed on Semi IP Hub.

How should engineers evaluate this Edge AI Accelerator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Edge AI Accelerator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.