CRYSTALS Kyber core for accelerating NIST FIPS 203 Key Encapsulation Mechanism

eSi-Kyber is a hardware accelerator core designed to accelerate post-quantum Key Encapsulation Mechanism (KEM) as defined by NIST…

Overview

eSi-Kyber is a hardware accelerator core designed to accelerate post-quantum Key Encapsulation Mechanism (KEM) as defined by NIST FIPS 203.

Kyber, an integral part of the Cryptographic Suite for Algebraic Lattices (CRYSTALS), is an IND-CCA2-secure key encapsulation mechanism known as ML-KEM. Its security is derived from the complexity of solving the learning-with-errors (LWE) problem over module lattices.

CRYSTALS encompasses two cryptographic primitives: Kyber, a secure KEM, and Dilithium, a strongly EUF-CMA-secure digital signature algorithm.

Key features

- The core supports all operations defined in the FIPS 203 standard :

- ML-KEM.KeyGen

- ML-KEM.Encaps

- ML-KEM.Decaps

- This core supports all security levels defined in the FIPS 203 standard :

- ML-KEM-512

- ML-KEM-768

- ML-KEM-1024

- Operation times ~10us for ML-KEM-1024 at 1GHz

- Includes optional external interface to access the internal SHA3/SHAKE function, fully supporting FIPS 202 standard

- Configurable arithmetic unit architecture for achieving the required performance and silicon area

- Constant time operations for resistance against time analysis attacks

- Simple generic control/data interface for controlling the core and loading input and unloading output data sets.

- ASIC or FPGA target

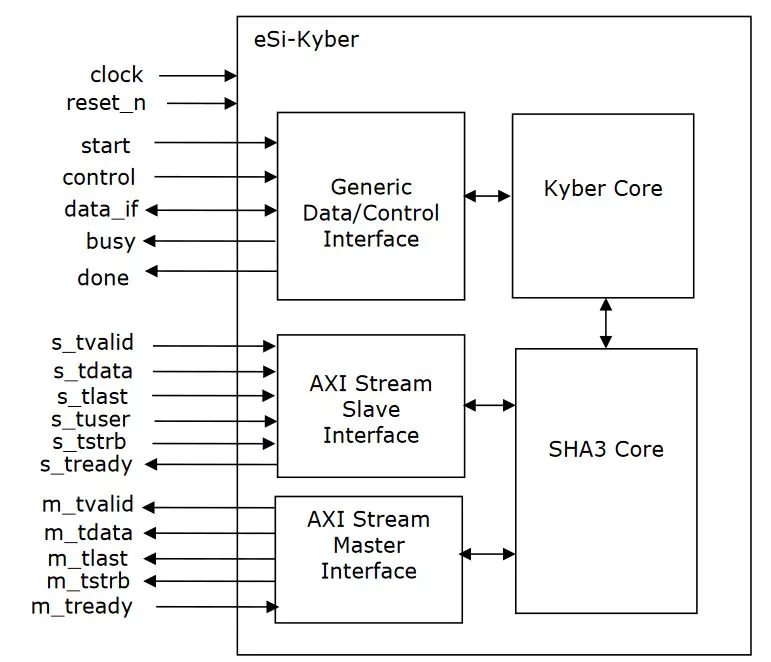

Block Diagram

Applications

- Automotive

- Datacentres

- Networking

- Space

- Military

- Industrial IoT

- Medical

- Telecommunications

- Banking

- Government

What’s Included?

- System Verilog RTL

- Testbench

- C Model

- Software libraries

Specifications

Identity

Provider

Learn more about Post Quantum IP core

How to design secure SoCs Part IV: Runtime Integrity Protection

Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

Deploying StrongSwan on an Embedded FPGA Platform, IPsec/IKEv2 on Arty Z7 with PetaLinux and PQC

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

Why Anti-tamper Sensors Matter: Agile Analog and Rambus Deliver Comprehensive Security Solution

Frequently asked questions about Post-Quantum Cryptography IP cores

What is CRYSTALS Kyber core for accelerating NIST FIPS 203 Key Encapsulation Mechanism?

CRYSTALS Kyber core for accelerating NIST FIPS 203 Key Encapsulation Mechanism is a Post Quantum IP core from EnSilica listed on Semi IP Hub.

How should engineers evaluate this Post Quantum?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Post Quantum IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.