ML-DSA Digital Signature Engine

The KiviPQC™-DSA is a hardware accelerator for post-quantum cryptographic operations.

Overview

The KiviPQC™-DSA is a hardware accelerator for post-quantum cryptographic operations. It implements the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 204. This mechanism realizes the appropriate procedures for securely generating a private/public key pair, digitally signing a message or a data block, and performing digital signature verification. The KiviPQC™-DSA supports all these procedures, making it suitable for both (signatory/verifier) sides.

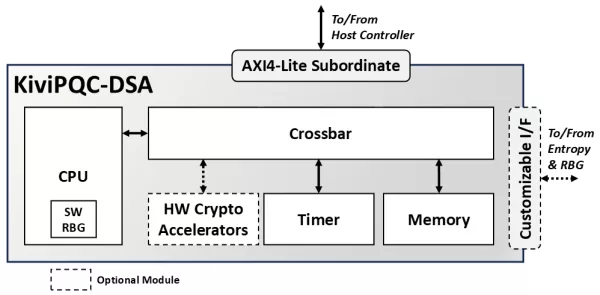

The engine supports all three parameter sets for ML-DSA, i.e. ML-DSA-44, ML-DSA-65, and ML-DSA-87. It is based on a RISC-V-like SoC topology, including a 32-bit RISC-V based processor. Designed for straightforward integration, communication with the host is accomplished via an AMBA® AXI4-Lite Subordinate port.

Two versions are available: a Fast (F) and a Tiny (T) version. The Fast (F) includes hardware crypto accelerators, a hardware timer module, and a crossbar interconnect module for internal data routing. The Tiny (T) version is a more compact architecture, targeting low area, with no hardware crypto accelerators. Both versions are currently offered with a software implementation of a Random Byte Generator (RBG), however, they are able to be integrated with an external (third-party) entropy source and RBG, via a fully customized interface, depending on the entropy/RBG selection.

The KiviPQC™-DSA provides hardware acceleration for computationally intensive operations while maintaining a small footprint and can be integrated into any system-on-chip (SoC) for ASIC or FPGA implementation. Beyond that, it combines a minimal attack surface with modest resource requirements for future-proof and quantum-safe systems.

Key features

NIST FIPS Compliant

- Module Lattice-based Digital Signature Algorithm (ML-DSA)

- NIST FIPS 204

- All three ML-DSA parameter sets

- 44 / 65 / 87

Versions

- Fast (F): Enhanced performance, with balanced area

- Tiny (T): Compact architecture, targeting low area

Enhanced Security

- Self-contained engine with a minimal attack surface

- Protection against timing-based side channel attacks

Resource-efficient Acceleration

- Hardware offloading and acceleration of time-consuming PQC operations

- 600MHz, with 83k or less eq. gates in modern ASICs (F)

- Minimal logic utilization

- 35k or less eq. gates, at 100MHz in modern ASICs (T)

Straightforward SoC Integration

- Lightweight, simple-control AMBA® AXI4 Interface

- Re-usable design, LINT-clean

Block Diagram

Applications

- The KiviPQC™-DSA realizes a quantum-safe digital signature mechanism between two parties (signatory and verifier) communicating over a public channel. The signatory generates a private/public key pair. Next, using the private key, the signatory signs a message or data block (and optionally a context string). Then, the verifier, employing the public key (and optionally the context string) verifies the signature. Sending the signed message, accompanied with the signatory’s public key, to the verifier, as well as the context string, is not part of the ML-DSA quantum-safe digital signature mechanism.

- The ML-DSA mechanism is meant to replace RSA and ECDSA across the ecosystem wherever digital signatures are required — from websites, emails, and blockchains, to IoT, government ID systems, and secure updates. The KiviPQC™-DSA engine thus offers quantum-resistant security for a wide range of applications. It is suited for secure SoCs that need long-term protection against quantum attacks in critical applications such as TLS/SSL acceleration for secure web and cloud services, software and firmware signing for operating systems and IoT devices, secure VPN and messaging protocols, blockchain transaction signing, and digital identity solutions for e-government and enterprise systems.

What’s Included?

The core is available in RTL (System Verilog) source code.

Its deliverable package includes the following:

- Self-checking HDL testbench

- Hardware Abstraction Layer (HAL) and driver for the application processor

- Sample simulation & synthesis scripts

- User documentation

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Post Quantum IP core

How to design secure SoCs Part IV: Runtime Integrity Protection

Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

Providing protection against EMFI attacks

Deploying StrongSwan on an Embedded FPGA Platform, IPsec/IKEv2 on Arty Z7 with PetaLinux and PQC

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

Frequently asked questions about Post-Quantum Cryptography IP cores

What is ML-DSA Digital Signature Engine?

ML-DSA Digital Signature Engine is a Post Quantum IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Post Quantum?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Post Quantum IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.