TES Electronic Solutions GmbH Provides a Configurable Display Controller IP for Flexible Embedded Video Applications

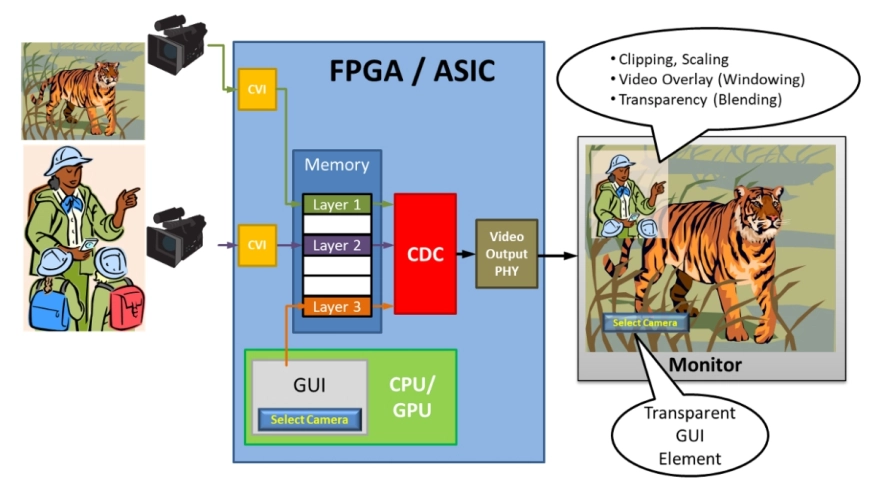

May 5, 2026 -- TES Electronic Solutions GmbH announces the availability of the Configurable Display Controller (CDC) IP core family, a scalable and modular solution designed to support a wide range of embedded display applications. The CDC enables developers to efficiently manage video- and image-composition, blending, and output in systems ranging from FPGA-based platforms to application-specific ASICs.

The CDC supports resolutions up to 16k (4096x4096 pixels) and delivers a MIPI-DPI compliant parallel video output, making it compatible with common display interface controllers such as HDMI, MIPI-DSI, 3G-SDI, and Video DACs. By combining multiple image layers, such as video feeds, graphics, or GUI elements, the CDC can generate a composed output stream on demand, supporting both continuous full-screen as well as on-demand partial-screen updates.

The CDC supports resolutions up to 16k (4096x4096 pixels) and delivers a MIPI-DPI compliant parallel video output, making it compatible with common display interface controllers such as HDMI, MIPI-DSI, 3G-SDI, and Video DACs. By combining multiple image layers, such as video feeds, graphics, or GUI elements, the CDC can generate a composed output stream on demand, supporting both continuous full-screen as well as on-demand partial-screen updates.

Use Cases and Applications

The CDC is designed to meet the needs of diverse embedded systems, particularly those requiring real-time image composition and flexible video output. Key applications include:

- Multi-source Video Overlays: In systems integrating multiple video inputs, such as surveillance or automotive infotainment, CDC enables the composition of camera feeds, navigation data, or user interfaces onto a single display. For example, a vehicle dashboard can show a camera view in the main area with a navigation overlay in the corner, using configurable windowing and blending to manage layer placement and transparency.

- Human-Machine Interfaces (HMI): The CDC supports the integration of graphics and real-time video in industrial control panels, medical devices, consumer electronics, and low-power wearables. It allows for partial screen updates, reducing processing-, bandwidth- and power-overhead while maintaining consistent visual output.

- Embedded Displays with Custom Video Processing: The CDC’s ability to handle 8-bit indexed and alpha-blended layers enables efficient rendering of GUI elements alongside video streams. Its support for colour correction, dithering, and gamma adjustment ensures the final output matches the characteristics of the connected display.

- Safety-Critical and Networked Systems: The CDC supports composition capture, allowing the processed image to be written back to memory. This is useful in systems where video must be sent over a network to a remote monitor or used in self-test routines for validation.

- Modular System Design: The CDC family includes members (CDC-200 to CDC-500) with increasing feature sets, allowing developers to select a base IP and add only the necessary functionality. The number of available input-layers and features such as scaling, YCBCR input/output, and image rotation are configurable at synthesis time, enabling optimized resource usage for each target application.

Key Functionalities

The CDC supports:

- Multiple layers with configurable blending modes (including alpha and constant alpha)

- Real-time blending, cropping, and windowing

- Support for various input formats (e.g. RGB, ARGB, AL, YCBCR) and output in RGB888 or YCBCR

- Programmable resolution via external PLL

- Flexible memory access with configurable bus interfaces (APB, AHB/AXI4, Avalon)

- Dithering and gamma correction to improve visual quality

- On-the-fly horizontal and vertical mirroring

Advanced features such as on-the-fly image rotation, dual-view operation, frame capture, or AXI-4 Streaming Input are available in higher-tier variants like the CDC-500, providing scalability for more complex systems.

Integration and Development Support

The CDC is designed for seamless integration into SoC architectures. Its asynchronous triple-clock domain design supports high bus latency and allows operation across different clock domains. A comprehensive configuration tool allows convenient definition of the required CDC configuration and computation of the resulting memory bandwidth requirements.

Software support includes a plain ANSI-C driver with comfort functions. The driver is reentrant, thread-safe, and require minimal OS dependencies, making them suitable for bare-metal or real-time environments.

Explore Display Controller IP:

Footprint and Efficiency

The CDC's footprint is highly dependent on configuration. A minimal CDC-200 implementation with one layer and no scaling or YCBCR support consumes approximately 1000 ALMs on an Intel Arria10 FPGA or 15-20k ASIC gates. Resource usage can be further reduced by disabling unused features at synthesis time.

Availability

The CDC IP is available now for licensing. Customers can select from the CDC-200 to CDC-500 family and configure features based on their specific application requirements.

For more information on this and other digital IP solutions,

visit the TES Customizable Display Controllers page.

Contact

For inquiries, please email graphics@tes-dst.com

About TES

With over 20 years of experience in ASIC design and embedded graphics IP, TES is a one-stop partner for high-performance semiconductor solutions. Our IP portfolio includes highly customizable 2D, 2.5D, and 3D GPUs, display controllers, and a wide range of analog and digital IP blocks, ranging from SiGe RF to industrial ASIC solutions.

Headquartered near Stuttgart, Germany, TES Electronic Solutions GmbH serves a global customer base, with design operations in Stuttgart and graphics IP development in Hamburg. Learn more at www.tes-dst.com.

Related Semiconductor IP

- Customizable Display Controller IP

- Display Controller

- LCD Display controller

- Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- Display Controller – LCD / OLED Panels (Avalon Bus)

Related News

- Digital Blocks DB9000 Display Controller IP Core Family Extends Leadership in 8K, Automotive, Medical, Aerospace, and Industrial SoC Designs

- TES offers CAN Flexible Data-Rate Controller IP Core for System-on-Chip (SoC) Designs

- Display Port/eDisplay Port v.1.4 Tx-Rx PHY & Controller Silicon Proven IP Cores with high Bandwidth and 4K/8K Resolution is ready for immediate licensing

- Unleashing the Full Potential of Your Display: eDisplayPort v1.4 PHY and Controller IP Cores are available for licensing for your Robust products

Latest News

- Arm delivers record-breaking quarter and full-year results

- SEMIFIVE and ICY Tech Achieve Successful Tape-out of 8nm eMRAM-Based Edge AI SoC, Targeting First Commercialization in Asia

- QuickLogic to Showcase EOS™ S3 and eFPGA Solutions at Sensors Converge

- Rambus Introduces PCIe® 7.0 Switch IP with Time Division Multiplexing for Scalable AI and Data Center Infrastructure

- Siemens hardware-assisted verification validates Arm AGI CPU for scalable agentic AI