Tenstorrent releases RiescueD, a powerful framework for writing direct tests in RISC-V assembly

September 2, 2025 -- Over the coming months, Tenstorrent plans to open source a suite of tools under the RiESCUE umbrella, which provides a suite of python scripts and libraries for generating RISC-V tests.

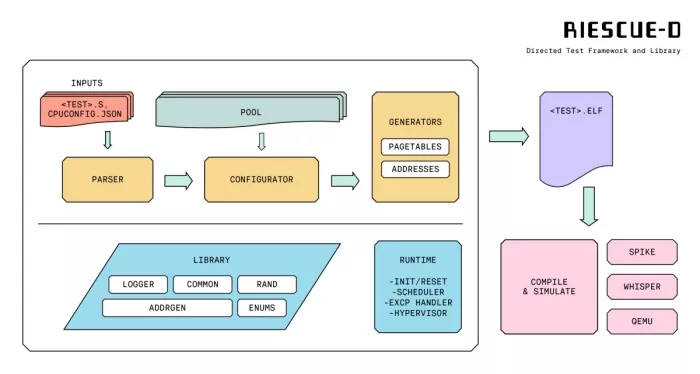

Tenstorrent would first like to announce the release of RiescueD, the RiESCUE Directed Test Framework. This is a powerful framework for writing directed tests in RISC-V assembly and provides library for test generator development, with features including:

- Randomization: Random data and address generation

- Memory Management: Automatic page table generation and memory mapping

- Environment Simulation: Support for various privilege modes, paging modes, and virtualization

- OS Code Simulation: Pseudo OS for scheduling and exception handling

RiescueD works well with several popular RISC-V simulators:

- Spike: RISC-V ISA simulator

- Whisper: Tenstorrent’s RISC-V Simulator

- QEMU: Full system emulation (coming soon)

Learn more about getting started with installation and setup, check out the RiescueD User Guide, or visit our GitHub repository for source code, examples, and more information.

Related Semiconductor IP

- RISC-V CPU IP

- Future-proof IP for training and inference with leading performance per watt and per dollar

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

Related News

- Ashling Announces RiscFree™ Debug and Trace Support for Tenstorrent TT-Ascalon™ RISC-V CPUs

- Tenstorrent Productizes RISC-V CPU And AI IP

- Tenstorrent and AutoCore Announce Strategic Partnership to Power High-Performance RISC-V Automotive Computing with AutoCore.OS

- Artisan Components Qualifies Libraries For PrimeTime SI

Latest News

- Silicon Creations Celebrates 20 Years of Global Growth and Leadership in 2nm IP Solutions

- TSMC Debuts A13 Technology at 2026 North America Technology Symposium

- Cadence Collaborates with TSMC to Accelerate Design of Next-Generation AI Silicon

- Synopsys Partners with TSMC to Power Next-Generation AI Systems with Silicon Proven IP and Certified EDA Flows

- JEDEC® Previews LPDDR6 Roadmap Expanding LPDDR into Data Centers and Processing-in-Memory