Digital Core Design Announces SPI master slave enhanced with detectors

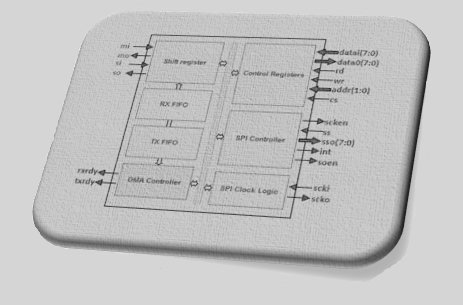

Oct 7th, 2013 -- The DSPI_FIFO is a fully configurable SPI master/slave device, which allows to configure polarity and phase of a serial clock signal SCK. DCD’s core enables microcontroller to communicate with serial peripheral de-vices, but also to communicate with an interprocessor in a multi-master system. It supports all the features of SPI and transmission/reception FIFOs, to significantly reduce the CPU time.

The DSPI_FIFO system is flexible enough, to interface directly with numerous standard product peripherals, even from several manufacturers. The system can be configured as a master or as a slave device, with data rates as high as CLK/4. The clock control logic allows to select clock polarity and choose two fundamentally different clocking protocols, to accommodate most available, synchronous serial peripheral devices. When the SPI is configured as a master, the software selects one of eight different bit rates for the serial clock. – A serial clock line (SCK) synchronizes shifting and sampling of the information on two independent serial data lines – explains Jacek Hanke, CEO at Digital Core Design – so the data is simultaneously transmitted and received.

The DSPI_FIFO automatically drives selected by the SSCR (Slave Select Control Register) slave outputs (SS7O – SS0O) and addresses the SPI slave device to exchange serially shifted data. Error-detection logic is included to support interprocessor communication.

A write collision detector indicates, when an attempt is made to write data to the serial shift register, while a transfer is in progress. A multiple-master mode-fault detector automatically disables DSPI output drivers, if more than one SPI device simultaneously attempts to become a bus master.

The DSPI_FIFO supports two DMA modes: single transfer and multi-transfer. These modes allow the DSPI_FIFO to interface to higher performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers.

DCD’s IP Core is technology independent and silicon proven design. It is fully customizable, which means it is delivered in the exact configuration of customer’s requirements. - There is no need to pay extra for not used features and wasted silicon – ends Hanke. The DSPI_FIFO includes fully automated testbench with complete set of tests allowing easy package validation at each stage of SoC design flow.

Detailed information: http://dcd.pl/ipcore/125/dspi-fifo/

Related Semiconductor IP

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- AHB-Lite Slave to SPI Master

- Master and Slave SPI Bus Controller

- SPI Controller IP- Master/ Slave, Parameterized FIFO, Avalon Bus

- APB SPI (Serial Peripheral Interface) master and slave

Related News

- Logic Fruit Technologies Launches LIN Master Slave IP Core

- CAST Introduces PDM-to-PCM IP Core for Easy Interfacing of Digital Microphones with SoCs

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Digital Blocks Announces the DB-I2C Controller IP Core with the availability of Master-Slave, Master, and Slave Versions for the AMBA 2.0 APB Interconnect

Latest News

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory

- M31 Collaborates with TSMC to Achieve Tapeout of eUSB2V2 on N2P Process, Advancing Design IP Ecosystem

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs

- Silicon Creations Celebrates 20 Years of Global Growth and Leadership in 2nm IP Solutions

- TSMC Debuts A13 Technology at 2026 North America Technology Symposium