DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

April 21, 2026 -- DCD-SEMI introduces a new CryptOne extension supporting EdDSA25519 signatures and X25519 key exchange, delivering high security, low latency, and efficient hardware implementation for modern SoC and FPGA designs.

Key highlights

Hardware support for EdDSA25519 and X25519 based on Curve25519

Hardware support for EdDSA25519 and X25519 based on Curve25519- Optimized size-to-performance ratio for embedded and FPGA systems

- Built-in resistance to side-channel attacks

- Compliance with RFC 7748 and RFC 8032 standards

- Verified in simulation and FPGA environments

Advanced cryptography in hardware

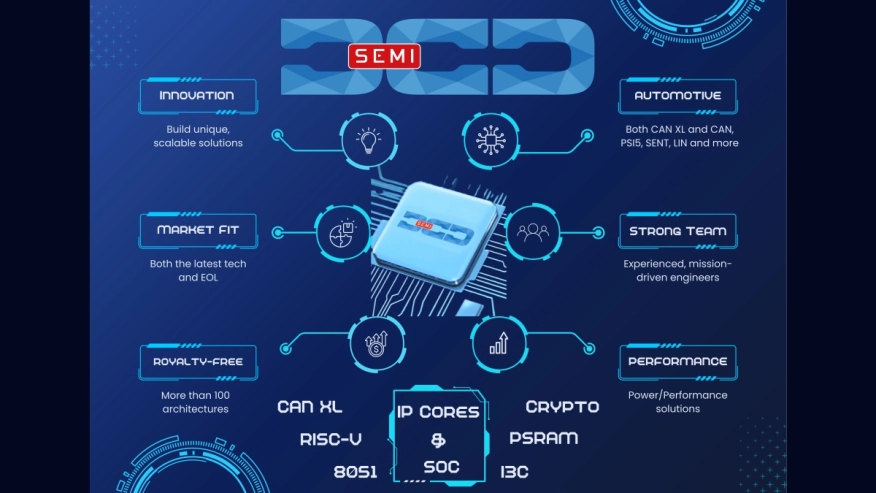

DCD-SEMI has expanded its CryptOne cryptographic co-processor with a new EdDSA Curve25519 IP core, bringing hardware acceleration to widely used elliptic-curve cryptography. The implementation is based on Curve25519, a 255-bit curve known for its efficiency, compact arithmetic, and strong security properties.

The extension enables fast and reliable execution of X25519 key agreement and EdDSA25519 digital signatures, making it particularly suitable for secure communications in constrained embedded environments.

Optimized architecture for performance and efficiency

Unlike general-purpose processors, CryptOne is a configurable IP core tailored to specific customer requirements. The Curve25519 module integrates directly into the existing architecture through dedicated hardware instructions, modular arithmetic accelerators, and optimized control logic.

This design minimizes latency while reducing silicon area and energy consumption. By simplifying arithmetic operations and eliminating unnecessary branching, the implementation achieves predictable execution flow—an important factor for both performance and security.

Explore Public Key IP:

Built with security in mind

The solution leverages Edwards-curve cryptography, which offers more regular computation patterns compared to traditional approaches. This reduces the risk of timing-based side-channel attacks and improves overall robustness in hardware implementations.

Alignment with industry standards, including RFC 7748 and RFC 8032, ensures interoperability and readiness for deployment in modern cryptographic systems.

Verified and deployment-ready

The development process included algorithm modeling, HDL implementation, and extensive verification using automated test environments. The IP core was validated against RFC-compliant test vectors and tested in simulation and FPGA setups to confirm correctness and optimization.

The result is a production-ready solution designed for security-critical applications across IoT, automotive, telecommunications, FinTech, cloud infrastructure, and industrial systems.

Related Semiconductor IP

- EdDSA Curve25519 signature generation engine

- Fast Public Key Engine with DPA or with DPA and FIA

- Agile PQC Public Key Accelerator

- Agile Post Quantum Crypto (PQC) Public Key Accelerator - NIST algorithms

- Agile ECC/RSA Public Key Accelerator with 32-bit ALU

Related News

- DCD-SEMI Brings Full ASIL-D Functional Safety to Entire Automotive IP Cores Portfolio

- DCD-SEMI Unveils Ultra-Fast DAES IP Core for AES Encryption

- Digital Core Design in cooperation with DCD-SEMI Unveils DCAN-XL: Revolutionary CAN XL IP Core Bridging the Gap Between CAN FD and Ethernet

- DCD-SEMI Joins MIPI Alliance and Unveils Latest I3C IP at MIPI Plugfest Warsaw 2025

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard