Perceptia Begins Port of pPLL03 to Samsung 14nm Process Technology

Sydney, Australia — November 25, 2025 — Perceptia Devices, a leader in low-jitter clocking IP, today announced the commencement of a port of its proven pPLL03 phase-locked loop (PLL) to Samsung Foundry’s 14LPU process node. This marks another milestone in Perceptia’s ongoing strategy to make its silicon-proven PLL solutions available across a wide range of advanced semiconductor platforms.

The pPLL03 is Perceptia’s low jitter, high-performance PLL IP core targeted at demanding SoC applications including AI accelerators, microprocessors, ADC/DAC sampling clocks, and high-speed digital subsystems. The port to Samsung’s 8LPU process forms part of Perceptia’s ongoing strategy to deliver robust, silicon-proven clocking solutions across leading-edge foundry technologies.

Key features of pPLL03 include:

- Maximum output frequency: Up to 4 GHz in Samsung 14 LPU

- Peak jitter: <5.2 ps (2.1 % of the output clock cycle) under supported operating conditions

- Full fractional multiplication of the input clock (12 bit resolution)

- Fast lock time (400 reference clock cycles)

- Fractional output division for rapid frequency change with glitch-less transition and 6 bit fractional resolution suitable for dynamic frequency scaling

- Low area and power to support applications with individual PLLs supporting many clock domains

- Robust behaviour across process, voltage, and temperature extremes

Samsung’s 14LPU process is based on FinFET technology and provides improved power and area efficiency over its bulk CMOS predecessors. The pPLL03 port will take advantage of process-specific enhancements to ensure optimal analog performance, low-noise operation, and ease integration with contemporary digital SoC design flows.

“Expanding our IP portfolio to Samsung’s 14LPU process reflects our commitment to supporting customers on multiple foundry platforms,” said Julian Jenkins, CEO at Perceptia Devices. “The pPLL03 is a proven solution that addresses the performance and power needs of modern digital SoCs, and bringing it to Samsung’s 14LPU will give customers more flexibility and lower integration risk.”

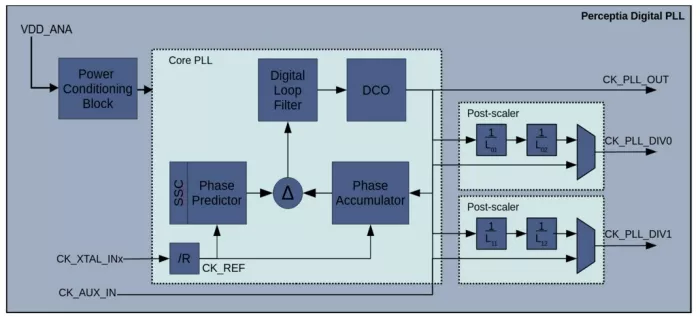

Perceptia’s all digital PLL architecture is uniquely suited for FinFET technologies, replacing finicky analog circuits with DSP calculations. In addition, Perceptia’s development methodology includes rigorous analog/mixed-signal simulation, comprehensive verification, and silicon characterisation. Ensuring the pPLL03 port to Samsung 14LPU will result in a production ready PLL.

The front end design kit for pPLL03 in Samsung 14LPU is available immediately to qualified licensees and includes:

- Liberty (.lib) timing models

- Verilog and Verilog-A simulation models

- Integration guidelines and layout constraints

The complete design kit will be available in Q1 2026 and will add the following to the front end design kit:

- GDSII and LEF physical views

- CDL netlist

Early access and customisation engagements are available for qualified customers.

About pPLL03

pPLL03 is a compact, low-jitter phase-locked loop (PLL) IP core optimised for advanced process nodes. Delivering output clock frequencies up to 5GHz, pPLL03 is designed for use in a wide range of high-performance applications including high-performance computing, AI acceleration and timing-critical logic, it delivers superior jitter and integration flexibility. pPLL03 is especially suited for designs with many clock domains. pPLL03 enables designers to confidently implement advanced timing architectures without compromising on area or power.

About Perceptia Devices

Perceptia Devices is an IP and design services provider, based in Sydney, Australia. With a focus on PLLs and precision timing, Perceptia supports customers across a wide range of applications including wireless communications, AI/ML, data converters, IoT, and mixed-signal SoCs with high performance, low area PLLs. For more information or to request the datasheet, please contact:

Related Semiconductor IP

- All Digital Fractional-N PLL for Performance Computing in Samsung 14LPP

- Low Power All Digital Fractional-N PLL in Samsung 14LPP

- Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Integer PLL on Samsung 8nm LN08LPP

- Integer PLL on Samsung 28nm LN28FDS

Related News

- Perceptia confirms performance of 11-GHz 0.4-ps 40-nm DSP-based PLL hard IP Core

- Perceptia Joins GlobalFoundries FDXcelerator Program to Bring PLL Technology to Portable Devices

- Perceptia Second-Generation Digital PLL IP Enters Mass Production

- Samsung Electronics Unveils Plans for 1.4nm Process Technology and Investment for Production Capacity at Samsung Foundry Forum 2022

Latest News

- Quintauris and Elektrobit Partner to Enable Reliable RISC-V Solutions for Automotive

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3