Perceptia 正式启动将 pPLL03 移植至三星 14 纳米工艺

2025 年 11 月 25 日,澳大利亚悉尼 -- 行业领先的低抖动时钟 IP 供应商 Perceptia Devices 公司今日宣布,已正式启动将其 pPLL03 锁相环 IP 向三星 14 纳米(Samsung 14LPU)工艺平台的移植工作。

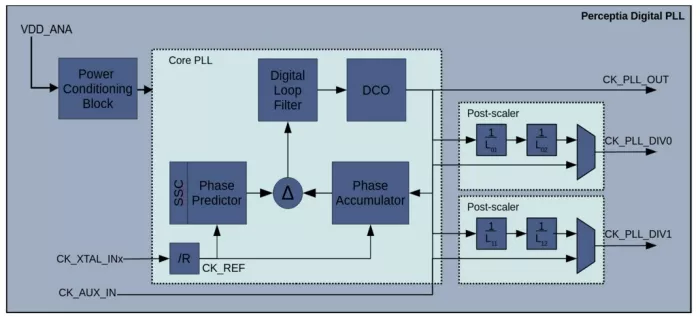

pPLL03 是 Perceptia 面向 AI 加速、微处理器、数模转换器采样时钟以及高速数字子系统等高性能应用场景研发 的超低抖动高性能锁相环 IP。Perceptia 致力于在行业领先工艺节点上为全球客户提供先进可靠,经过硅验证的 解决方案。此次向三星 14 纳米(Samsung 14LPU)节点的工艺移植正是推进这一战略布局的重要一步。

pPLL03 的关键参数包括:

- 频率输出范围:最高可达 4GHz,同时支持整数与分数 N 分频模式

- 峰值周期抖动:在 4GHz 输出时小于 2.1%周期(约 5.2ps)

- 锁定时间:仅约 400 个参考时钟周期

- 分数分频输出:支持无毛刺快速频率切换,具备 6bit 分数分辨率,适用于动态频率调节(DVFS)

- 小型化设计:将模拟电路模块所占面积大幅减少,便于同时使用多个片上 PLL

- 可靠性:在工艺、电压、温度(PVT)极限条件下均可稳定工作

三星 14LPU 工艺采用 FinFET 技术,相比其前代工艺在功耗控制与面积利用效率上均实现显著优化。此次 pPLL03 的移植将充分利用这些工艺升级,进一步优化其模拟性能与噪声表现,并实现 pPLL03 与行业前沿数字 SoC 设计流程的高效集成。

“三星 14 纳米(Samsung 14LPU)工艺在性能、器件密度和能效之间实现了优秀的平衡,这让它成为 先进 SoC 设计中一个极具吸引力的选择。”Perceptia Devices 首席执行官 Julian Jenkins 表示 “通过将 pPLL03 IP 推向该工艺节点,我们为客户在涵盖 5G、AI 加速器以及先进处理器等最具挑 战性的应用环境中提供可靠的高性能时钟解决方案。”

Perceptia 的全数字 PLL 架构与 FinFET 工艺高度适配,将复杂的模拟电路结构替换为数字信号处理 (DSP)与运算。同时,公司在 IP 开发和移植过程中采用条件严格的模拟及混合信号仿真、全面的性能验 证及硅片实测流程,确保 pPLL03 移植至三星 14LPU 工艺后具备量产级可靠性。

相关前端设计套件将即刻起对符合条件的客户开放获取,其中包含以下内容:

- Liberty(.lib)时序模型

- Verilog 与 Verilog-A 仿真模型

- 集成设计指南与版图约束说明

完整的设计套件预计将在 2026 年第一季度向客户开放,其中将包含:

- GDSII 与 LEF 版图

- CDL 网表

关于 pPLL03

pPLL03 是一款专为先进工艺节点优化设计的紧凑型低抖动锁相环(PLL)IP 核。该款 IP 输出频率范围可达 4GHz,其极佳的低抖动性能与优异的集成灵活性使其完美适配包括高性能计算、人工智能(AI)加速及时序敏感 逻辑在内的不同高性能高要求应用场景。pPLL03 尤其适用于为多时钟域提供时钟。它帮助设计人员在不牺牲面积 或功耗的前提下,构建先进可靠的高性能时序架构。

关于 Perceptia Devices

Perceptia Devices 总部位于澳大利亚悉尼,是行业领先的半导体 IP 和设计服务提供商。Perceptia 专注于 高速与超低功耗的混合信号芯片设计,致力于为无线通信、人工智能(AI/ML)、数据转换及混合信号 SoC 等多 领域客户提供时序精准、集成高效的解决方案。凭借深厚的技术积累和灵活的设计能力,Perceptia 在过去 20 余 年中助力客户加速产品开发,实现卓越性能。

如需了解更多产品信息或索取产品数据手册,您可以通过以下方式联系我们:

Related Semiconductor IP

- All Digital Fractional-N PLL for Performance Computing in Samsung 14LPP

- Low Power All Digital Fractional-N PLL in Samsung 14LPP

- Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Integer PLL on Samsung 8nm LN08LPP

- Integer PLL on Samsung 28nm LN28FDS

Related News

- Perceptia第二代数字PLL IP进入批量生产

- 三星电子在 2022 年三星代工论坛上公布 1.4nm 工艺技术及产能投资计划

- Perceptia Devices 正式启动将 pPLL03 移植至三星 8 纳米工艺平台

- Perceptia Devices 推出 pPLL08N:紧凑型窄带射频锁相环(RF PLL)系列 IP,进一步完善 pPLL08 产品线