Digital Core Design introduces Local Interconnect Network IP Core

Bytom -- January 31, 2013 -- The DLIN is the newest Local Interconnect Network IP Core developed by Digital Core Design. Polish IP Core provider has presented a solution, which is fully compatible with the LIN 1.3, 2.1 and the newest version 2.2 Revision A, released by the LIN Consortium.

The core is described at RTL level, empowering the target use in both, FPGA and ASIC technologies.

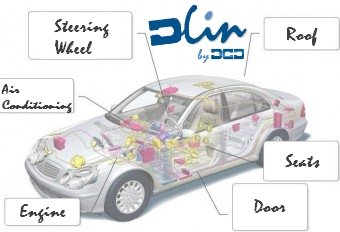

The DLIN, DCD’s IP Core for Local Interconnect Network, is an ideal solution most of all for automotive designs. As technologies and facilities implemented in a car grow every year, the need for a cheap serial network has arisen. That’s why LIN seems to be the most suit-able solution to integrate intelligent sensor devices or actuators in today’s cars. Contrary to the CAN, it enables cost competitive serial communication, building the same an extended vehicle’s electrical network, which… will be used as CAN’s sub-network. – Our DLIN controller supports transmission speed between 1 and 20kb/s – says Jacek Hanke, CEO in Digital Core Design – that allows to transmit and receive LIN messages compatible to LIN 1.3, LIN 2.1 and also the newest LIN 2.2 rev A.

Compared to the CAN, LIN is slower, but thanks to its simplicity, it is much more cost effective. That’s why the DLIN is ideal for communication in intelligent sensors and actuators, where the bandwidth and versatility of CAN is not required. DCD’s IP Core provides an interface between a microproces-sor/microcontroller and a LIN bus. It can work as a master or as a slave LIN node, depending on a working mode determined by the microprocessor/microcontroller. The reported information status includes the type and condition of transfer operations being performed by the DLIN, as well as a wide range of LIN error conditions (overrun, framing, parity, timeout). DCD’s IP Core includes also a pro-grammable timer, which allows to detect timeout and synchronization error. The Core is described at RTL level, empowering the target use in FPGA and ASIC technologies.

More information & data sheet: http://www.dcd.pl/ipcore/132/dlin/

KEY FEATURES:

- Conforms with LIN 1.2, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s

- Master and Slave work mode

- Time-out detection

- Extended error detection

- “Break-in-data” support

- Available system interface wrappers:

- AMBA - APB Bus

- Altera Avalon Bus

- Xilinx OPB Bus

Related Semiconductor IP

- GF 0.13um BCD LIN PHY IP, >20Kbps - GlobalFoundries 130nm

- Verification IP for LIN

- Host / device LIN controller IP

- LIN Verification IP

- LIN Synthesizable Transactor

Related News

- OPENEDGES NoC (Network on Chip) Interconnect IP & DDR Controller licensed by ASICLAND

- Arteris IP FlexNoC Interconnect and Resilience Package Licensed in Neural Network Accelerator Chip Project Led by BMW Group

- CAST Expands Security IP Portfolio with High Performance SM4 Cipher Core

- Creonic Updates Doppler Channel IP Core with Extended Frequency Band and Sampling Range

Latest News

- Bolt Graphics Completes Tape-Out of Test Chip for Its High-Performance Zeus GPU, A Major Milestone in Reducing Computing Costs By 17x

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory

- M31 Collaborates with TSMC to Achieve Tapeout of eUSB2V2 on N2P Process, Advancing Design IP Ecosystem

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs

- Silicon Creations Celebrates 20 Years of Global Growth and Leadership in 2nm IP Solutions