CAST Introduces MAC-SEC-MG IP Core for Secure 10G+ Ethernet SoC Designs

New multi-gigabit MACsec engine provides Ethernet security for 2.5G, 5G, 10G, and higher-bandwidth embedded systems at line speed

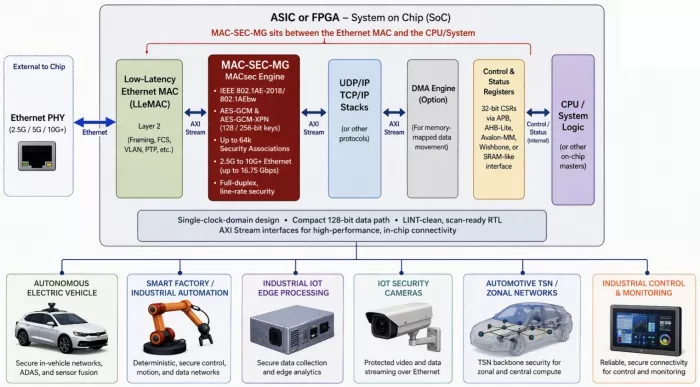

Woodcliff Lake, NJ — April 27, 2026 — CAST, a leading provider of semiconductor intellectual property cores, today announced the MAC-SEC-MG MACsec Protocol Engine IP core, extending the company’s secure Ethernet IP offerings with a multi-gigabit MACsec engine optimized for providing 10G+ Ethernet in ASIC and FPGA designs requiring secure channels.

The new MAC-SEC-MG core implements the IEEE 802.1AE MACsec standard in custom hardware, enabling designers to add strong Ethernet link security without the processing burden, latency, or integration complexity of software-based approaches. Optimized for networks operating from 2.5 Gbps to 10 Gbps and beyond, the core supports full-duplex line-speed operation of up to 16.75 Gbps.

The new MAC-SEC-MG core implements the IEEE 802.1AE MACsec standard in custom hardware, enabling designers to add strong Ethernet link security without the processing burden, latency, or integration complexity of software-based approaches. Optimized for networks operating from 2.5 Gbps to 10 Gbps and beyond, the core supports full-duplex line-speed operation of up to 16.75 Gbps.

The MAC-SEC-MG is well-suited to secure Ethernet links in automotive, industrial, IoT edge, and other embedded systems that increasingly rely on high-speed secure networks for real-time control, sensor aggregation, data movement, and external connectivity. It is especially attractive for designs that need standards-based confidentiality and integrity protection while preserving deterministic, hardware-level data flow.

“As embedded systems move to higher-speed Ethernet, designers need security that keeps pace without adding software overhead or disrupting system performance,” said Alexander Mozgovenko, product manager at CAST. “Our MAC-SEC-MG core gives SoC developers a practical, integration-ready way to add line-rate MACsec protection for 10+ Gbps links, while keeping implementation efficient and low risk.”

Standards-Based MACsec for Higher-Speed Embedded Ethernet

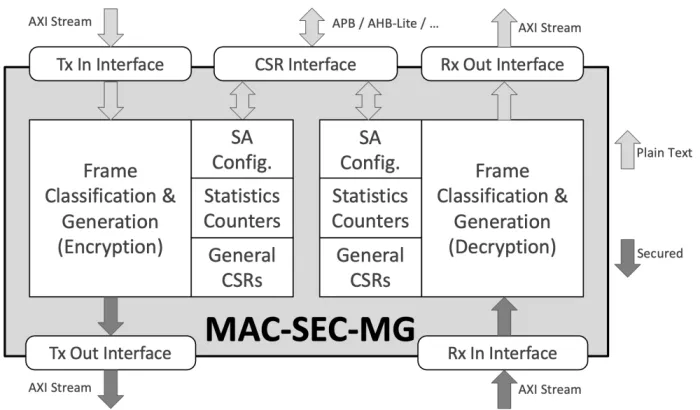

The MAC-SEC-MG core supports the key MACsec capabilities needed for modern secure Ethernet implementations, including AES-GCM and AES-GCM-XPN operation with 128- or 256-bit keys, support for multiple Security Channels and Security Entities, and a configurable number of Security Associations of up to 64k. It also supports VLAN-in-Clear operation for designs that require protected traffic with visible VLAN tagging.

To balance throughput and silicon efficiency, the core uses a compact 128-bit datapath and operates at full-duplex, line-speed in each direction. This makes it suitable for designers moving beyond 1G Ethernet to higher-bandwidth links while still needing a practical implementation footprint.

The MAC-SEC-MG Core for new SoCs provides full-duplex line-rate security up to 16.75 Gbps, with in-system protection between the Ethernet MAC and higher-layer protocol stacks.

Straightforward Integration with Ethernet and TSN-Based SoCs

Designed for easy system integration, the MAC-SEC-MG core is a fully synchronous, single-clock-domain design with standard interfaces and no multi-cycle or false timing paths. Control and status registers are accessed through a generic 32-bit memory-mapped slave interface, with bridges available for AMBA® APB, AHB-Lite, Avalon®-MM, and Wishbone host environments.

Packet data is carried over AXI-Stream interfaces with configurable data width, enabling direct connections to Ethernet MACs, PTP timestamping units, and higher-layer protocol engines within modern SoC architectures. Developers can shorten their time-to-market for secure Ethernet subsystems by having the MAC-SEC-MG core delivered pre-integrated with companion CAST offerings such as the Low-Latency Ethernet MAC, TSN Endpoint and Switch cores, and UDP/IP and TCP/IP hardware stacks.

Sourced from Fraunhofer IPMS and productized to CAST quality standards, the MAC-SEC-MG core is available as synthesizable RTL for ASIC and FPGA designs or as a targeted FPGA netlist, together with documentation, verification collateral, and implementation support materials needed for efficient deployment.

Explore MACsec IP:

Available Now

With the introduction of MAC-SEC-MG, CAST expands its security portfolio of products with a solution tailored to higher-speed embedded Ethernet applications. The core is available now for ASIC and FPGA designs. For technical details, evaluation options, or pricing, visit the MAC-SEC-MG product page or contact CAST.

Engineered by Fraunhofer IPMS.

Engineered by Fraunhofer IPMS.

Related Semiconductor IP

- MACsec Protocol Engine for 1G/10G+ Ethernet

- HPC MACsec Security Modules for Ethernet

- ASIL B / ISO 26262 and ISO 21434 Compliant 1G-25G MACsec Security Module

- P1619 / 802.1ae (MACSec) GCM/XTS/CBC-AES Core

- 1.6T/3.2T Multi-Channel MACsec Engine with TDM Interface (MACsec-IP-364)

Related News

- Fraunhofer IPMS develops new 10G TSN endpoint IP Core for deterministic high-speed Ethernet networks

- CAST Expands Security IP Portfolio with High Performance SM4 Cipher Core

- CAST Reaches 200 CAN IP Core Customers

- CAST Introduces JPEG XL Encoder IP Core for High- Quality, On-Camera Still-Image Compression

Latest News

- CAST Introduces MAC-SEC-MG IP Core for Secure 10G+ Ethernet SoC Designs

- Crypto Quantique and Attopsemi Unite PUF and I-fuse® OTP technology to Deliver Zero-Overhead Device Enrollment on FinFET Technology

- Arasan Announces immediate availability of its UFS 5.0 Host controller IP

- Bolt Graphics Completes Tape-Out of Test Chip for Its High-Performance Zeus GPU, A Major Milestone in Reducing Computing Costs By 17x

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory