Overview

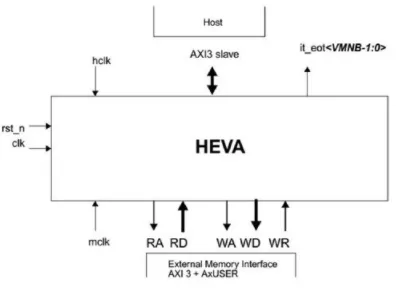

The Hardware Encoder Video Accelerator (HEVA), supports HEVC encoding low complexity with a flexible architecture targeting at least 1080p60 with minimal processing units and memory cuts and

up to 2160p120 with large number of units and large memory cuts.

Trade-off performance/area at design configuration: Reference cache size for 2160p30 at 350 MHz, 1 reference frame and bandwidth, overhead of 100% for references i.e. 1.5 GBytes/sec (minimal is 1.2 GB/s)

Hardware interfaces :Host interface AXI3/AXI4 slave interface for the registers and command/status FIFO, Memory interface AXI3/AXI4 Streaming interfaces to External DRAM, Asynchronous AXI3/AXI4 128 bits interface, Synchronous DMA arbiter and memory interface

Task sequencing modules: Manages communication and storage between processing modules, Control the shared memories and caches between the TPU modules and TSU/MIF, Defines the execution mode of the task processing units

Task processing modules: Perform the pixel and bit-stream processing under control of TCR/TSU, The number of processing elements is defined at design configuration to sustain the required

performance, A local reference cache is needed for performance for some processing units.

Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about Video Processing IP core

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

Configurable Processors for Video Processing SOCs

Programmable FPGA devices are the perfect choice for interfacing with multiple high-resolution image sensors simultaneously...

A look at the design of multiprocessor systems-on-chips (MPSoCs) for video applications and how to optimize them for computational power and real-time performance as well as flexibility. Part 1: Architectural approaches to video processing

Building a high-performance, quad-channel H.264 encoder using low-cost, low-power FPGA architecture.

Adding to its growing portfolio of licensable silicon IP subsystems, ARC has announced five configurable video processing subsystems. The subsystems range from the smallest-size AV 402V to the highest-performance AV 417V, and support multi-standard video encoding and decoding at resolutions ranging from CIF to D1.