USIM Verification IP

USIM Verification IP is a smart way to verify the USIM component of a SOC or ASIC.

Overview

USIM Verification IP is a smart way to verify the USIM component of a SOC or ASIC. The SmartDV's USIM Verification IP is fully compliant with standard USIM Specification. It supports all commands and file types. The USIM Verification IP monitor acts as powerful protocol-checker, fully compliant with USIM specification 3GPP TS 31.102 and ETSI TS 102 221. USIM Verification IP includes an extensive test suite covering all possible scenarios. It can perform all protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively. This way it detects violation of protocol completely.

USIM Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

USIM Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compliant with 3GPP TS 31.102 and ETSI TS 102 221 Specification.

- Supports USIM interface between Master and Slave.

- Supports specific command parameters.

- Supports file structures.

- Supports contents of Efs (Elementary Files).

- Supports security functions.

- Supports commonly used communication protocols

- T=0 for asynchronous half-duplex character transmission, and

- T=1 for asynchronous half-duplex block transmission

- Supports all functions for complete smart card sessions, including

- Card activation and deactivation

- Cold/Warm reset

- Answer to Reset (ATR) response reception

- Supports application protocol to be used on the interface between Master and Slave.

- Supports Authenticate, optional Get Identity commands.

- Monitor detects and notifies the testbench of significant events such as transactions, warnings, timings and protocol violations.

- Supports constraints Randomization.

- Status counters for various events on bus.

- Callbacks in transmitter, receiver and monitor for user processing of data.

- USIM Verification IP comes with complete test suite to test every feature of USIM specification.

- Functional coverage for complete USIM features

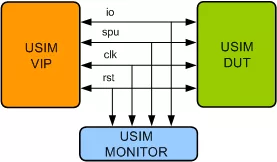

Block Diagram

Benefits

- Rich set of configuration parameters to control the functionality.

- Faster testbench development and more complete verification of USIM designs.

- Easy to use command interface simplifies testbench control and configuration of Master and Slave.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the USIM testcases.

- Examples showing how to connect various components, and usage of Master,Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is USIM Verification IP?

USIM Verification IP is a UART IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.