MECHATROLINK-III Master/Slave IP

MECHATROLINK-III Master/Slave IP together with CPU communicates with the products adapting.

Overview

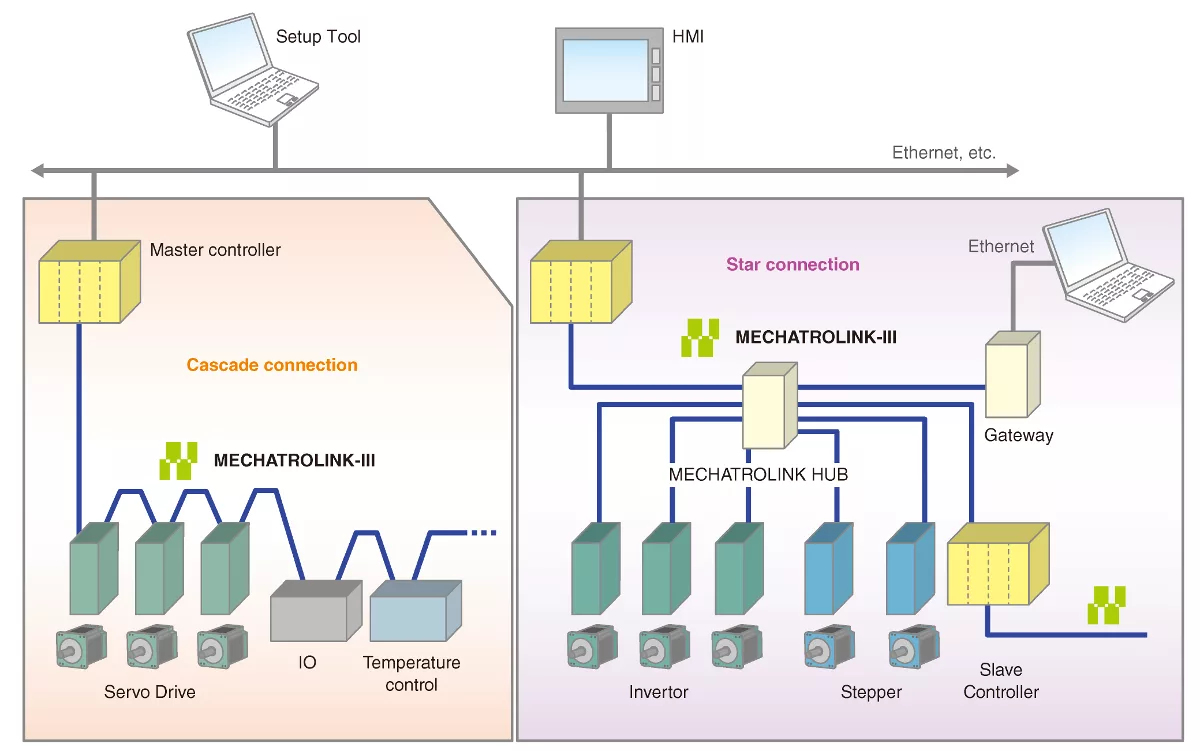

MECHATROLINK-III Master/Slave IP together with CPU communicates with the products adapting.

MECHATROLINK-III standardized by MECHATROLINK Members Association.

Supported Devices

- Cyclone V

- Texas Instruments Sitara™ (Single Slave)

Key features

- Functionally compatible with JL-100 which is the ASIC for MECHATROLINK-III Master/Slave communication.

- Parameters required for MECHATROLINK-III communication are set either by cpu or through external pins.

- Certified by MECHATROLINK Members Association.

Block Diagram

What’s Included?

- IP (Encrypted netlist)

- Reference design

- User’s manual

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is MECHATROLINK-III Master/Slave IP?

MECHATROLINK-III Master/Slave IP is a UART IP core from Macnica listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.