Simulation VIP for UART

Best-in-class UART Verification IP for your IP, SoC and system-level design testing.

Overview

Best-in-class UART Verification IP for your IP, SoC and system-level design testing. In production since 2014 on dozens of production designs.

Cadence provides a mature and comprehensive Verification IP (VIP) for the UART protocol. Incorporating the latest protocol updates, the Cadence® Verification IP for UART provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for UART helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog along with the Universal Verification Methodology (UVM).

Supported Specification: Standard UART 16550 Specification

Key features

- Mode

- Synchronous, Asynchronous

- Transmission Mode

- Full-Duplex, Half-Duplex

- Baud Rate

- Configurable baud rate generation

- Word Length

- Configurable word length (5, 6, 7, or 8-bits)

- Stop Bits

- Configurable stop bits (1, 1.5, or 2-bits)

- Error Detection Flags

- Overrun, Frame, and Parity error

- IDLE Frame Insertion/ Detection

- Supports IDLE frame insertion and detection on transmitter and receiver respectively

- TX/RX FIFOs

- Supports up to 128-bytes FIFO depth for both transmitter and receiver

- Auto Flow Control

- Supports hardware flow control

- Extended Features

- LIN, MODBUS, Driver Enable, IRDA, Smartcard, and LPUART

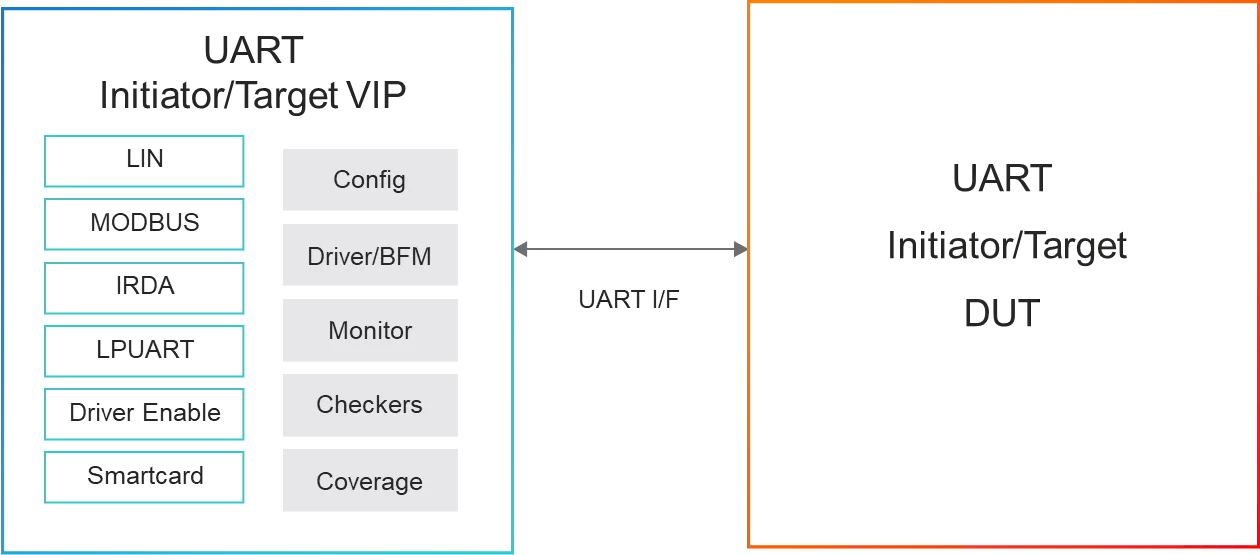

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is Simulation VIP for UART?

Simulation VIP for UART is a UART IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.