UART - Ensures reliable serial communication and protocol compliance in SoCs

The UART Verification IP provides a comprehensive solution for validating UART communication interfaces in System-on-Chip (SoC) d…

Overview

The UART Verification IP provides a comprehensive solution for validating UART communication interfaces in System-on-Chip (SoC) designs. It simulates both transmission and reception functionality to ensure data integrity.

This IP supports error injection, debugging tools, and protocol compliance checking. It is ideal for ensuring reliability and protocol compliance in UART-based peripherals used in various applications, from simple devices to advanced systems.

Key features

- Protocol Compliance: Ensures UART communication adheres to the standard protocol, including key parameters like baud rate, parity, data bits, and stop bits. This guarantees reliable and consistent data transmission across devices.

- Transmission & Reception Testing: Verifies the full functionality of UART interfaces by testing both the transmission and reception of data. This ensures that data is correctly sent and received, maintaining integrity under various conditions.

- Error Injection: Simulates real-world communication errors by injecting faults into the UART interface. This helps identify vulnerabilities and tests the system’s ability to recover from errors.

- Baud Rate, Parity, and Stop Bit Validation: Checks that the UART interface is correctly configured for baud rate, parity, and stop bits. This ensures that the communication settings are properly set for accurate and consistent data transfer.

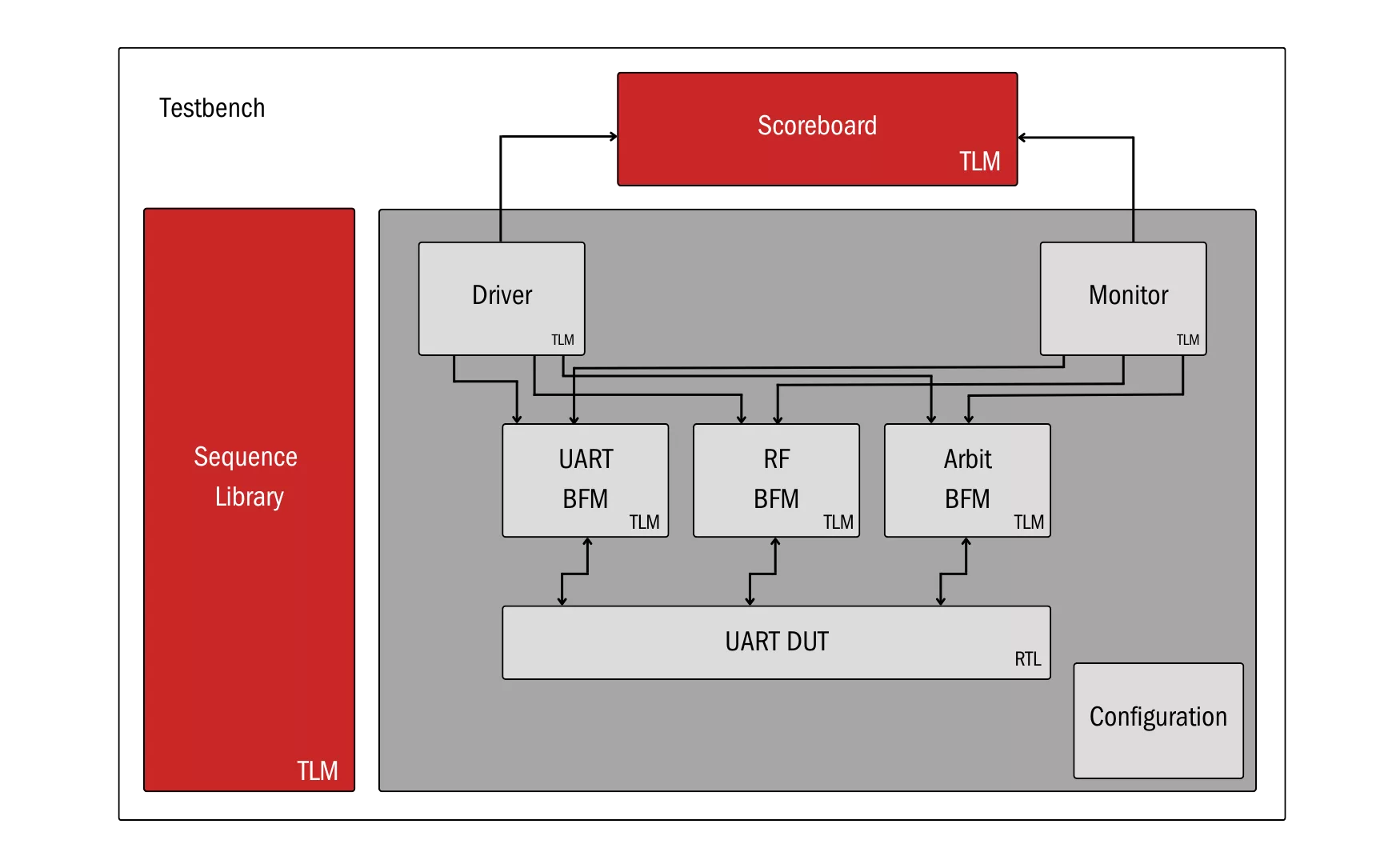

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is UART - Ensures reliable serial communication and protocol compliance in SoCs?

UART - Ensures reliable serial communication and protocol compliance in SoCs is a UART IP core from XtremeSilica listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.