UART/USART Verification IP

The UART /USART Verification IP provides an effective & efficient way to verify the components interfacing with UART/USART interf…

Overview

The UART /USART Verification IP provides an effective & efficient way to verify the components interfacing with UART/USART interface of an ASIC/FPGA or SoC. The UART/USART VIP is fully compliant with the Standard National Semiconductor PC16550D specification of UART/USART. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key features

- Available in UVM, System UVM, UVM.

- According to the National Semiconductor PC16550D Compliance.

- Supports Simplex and Duplex mode.

- Independently controlled transmit, receive, line status, and data set interrupts

- A programmable baud generator divides any input clock by 1 to (2^16 – 1) and generates baud clock according to the spec.

- Both 16x and 13x sample mode supported.

- Independent receiver clock input.

- Full duplex operation.

- MODEM control functions (CTS, RTS, DSR, DTR, RI and DCD).

- Fully programmable serial-interface.

- 5-, 6-, 7-, or 8-bit characters.

- Even, odd, or no-parity bit generation and detection.

- 1, 1.5 or 2 stop bit generation.

- UART/USART VIP can act as either UART/USART receiver or UART/USART transmitter in a transfer depending on the configurations set.

- Baud generation (DC to 1.5M baud).

- False start bit detection.

- Complete status reporting capabilities.

- Line breaks generation and detection.

- Configurable receiver FIFO depth.

- Reports various timing errors, which can be used to check any timing violations.

- Provides full control to the user to enable/disable various types of messages.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Transmitter and Receiver.

- Graphical analyzer to show transactions for easy debugging.

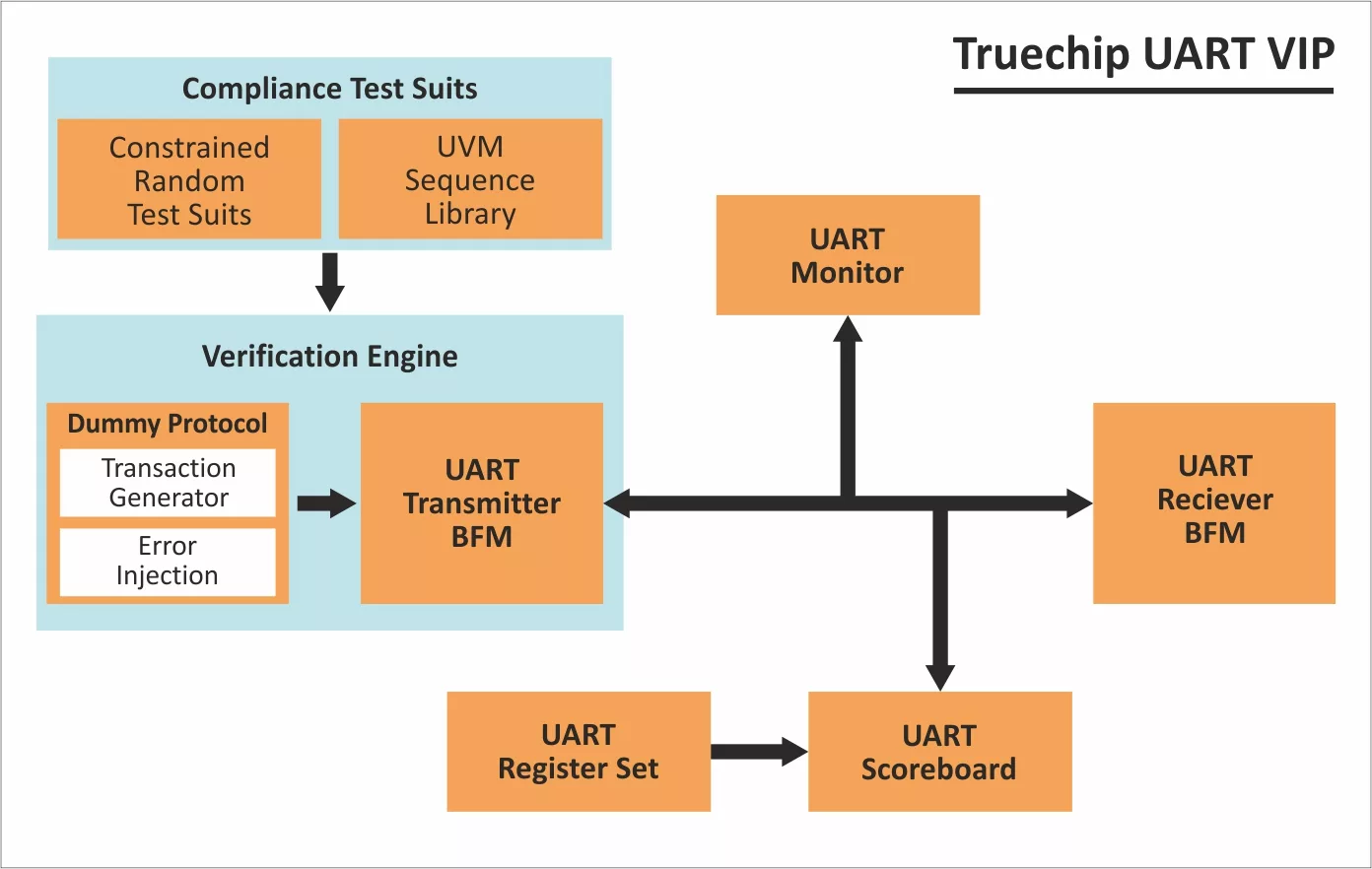

Block Diagram

What’s Included?

- UART/USART TRANSMITTER

- UART/USART Receiver

- UART/USART Monitor

- UART/USART Scoreboard

- Basic Test Suite

- Error Test Suite

- User Test Suite

- Integration Guide, User Manual, and Release Notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is UART/USART Verification IP?

UART/USART Verification IP is a UART IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.