USB 4.0 V2 PHY - 4TX/2RX, TSMC N3P , North/South Poly Orientation

The USB4 PHY IP provides designers with the industry's best combination of small area and low power with support for the process …

Overview

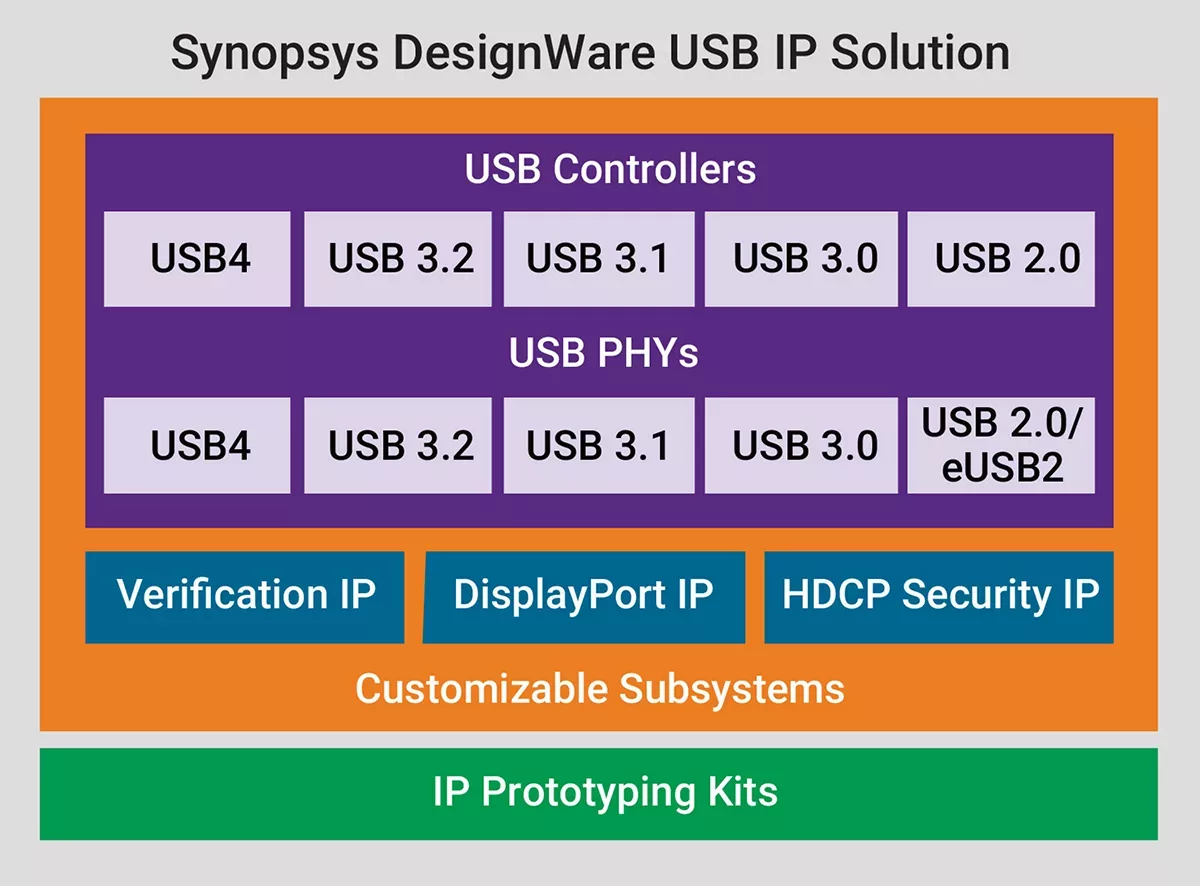

The USB4 PHY IP provides designers with the industry's best combination of small area and low power with support for the leading process technologies such as 5nm FinFET. The USB4 PHYs use a single efficient GDSII design that supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates.

The USB4 IP is designed to meet the functionality, power, performance, and area requirements of a broad range of storage, PC, and tablet SoC designs as well as software development debug and easy deployment of artificial intelligence (AI) applications at the edge.

The USB IP has shipped in billions of units for leading electronics companies worldwide. Using the USB IP significantly reduces development time and engineering risk, helping designers to bring USB-based SoCs to market faster.

The USB IP is the most certified IP solution in the industry. As the leading provider of USB IP for nearly two decades, the vendor is enabling designers to lower the risk and adoption barrier of integrating USB4 functionality into their SoCs.

Key features

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

- USB Type-C connectivity support available (external party Type-C Port Controller not included)

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 3nm | N3P | — |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB 4.0 V2 PHY - 4TX/2RX, TSMC N3P , North/South Poly Orientation?

USB 4.0 V2 PHY - 4TX/2RX, TSMC N3P , North/South Poly Orientation is a Single-Protocol PHY IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.