Open LVDS Display Interface (OpenLDI) Verification IP

Open LVDS Display Interface(OpenLDI) specification was developed through the cooperation of companies in the semiconductor, displ…

Overview

Open LVDS Display Interface(OpenLDI) specification was developed through the cooperation of companies in the semiconductor, display, computer system, connector, and cable industries to be an open standard for the digital connection of display sources and display devices. This standard is an evolution of the de facto industry standard for the connection of display controllers to LCD panels in notebook computers. The SmartDV VIP for OpenLDI is fully compliant with Standard Open LVDS Display Interface(OpenLDI) Specification.

Open LVDS Display Interface (OpenLDI) Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

Open LVDS Display Interface (OpenLDI) Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full OpenLDI Display Source and Display Device functionality.

- Supports OpenLDI v0.95 specification

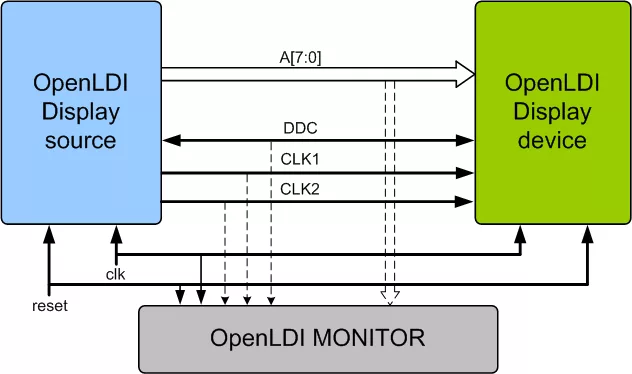

- Supports 8 serial data lines (A0 through A7) and two clock lines (CLK1 and CLK2) in the OpenLDI interface.

- Supports DDC2B protocol to retrieve the EDID data structure from display.

- Supports EDID 1.3 and 2.0 data structures in Display source and display devices.

- Supports Gamma Correction in Display source and display devices.

- Supports DC balanced and unbalanced modes of operation.

- Supports following RGB Pixel formats in DC balanced and unbalanced mode of operation,

- 18-bit single pixel

- 24-bit single pixel

- 18-bit dual pixel

- 24-bit dual pixel

- Supports Intra-pair and Inter-pair Skew insertion and detection

- Supports the following common display resolutions

- 640 x 480

- 800 x 600

- 1024 x 768

- 1280 x 1024

- 1600 x 1024

- 1600 x 1200

- 1920 x 1080

- 1900 x 1200

- 2048 x 1536

- Supports user controlled Default Configurations of video formats for a Display Source and display devices.

- Supports full plug and play using hot plug operation and detect device or source attach and removal events.

- The model has a rich set of configuration parameters to control OpenLDI functionality.

- Callbacks in Display Source, Device and monitor for user processing of data.

- Status counters for various events in bus.

- Notifies the test bench of significant events such as transactions, warnings, and protocol violations.

- The source is capable of inserting various transmit errors.

- The display device is capable of detecting various errors.

- OpenLDI Verification IP comes with complete test suite to verify each and every feature of OpenLDI specification.

- Functional coverage for complete features.

Block Diagram

Benefits

- Faster test bench development and more complete verification of OpenLDI designs.

- Easy to use command interface simplifies test bench control and configuration of OpenLDI display source and display device.

- Simplifies results analysis.

- Runs in every major simulation environment

What’s Included?

- Complete regression suite containing all the OpenLDI testcases.

- Examples showing how to connect various components, and usage of OpenLDI Display source,display device and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Open LVDS Display Interface (OpenLDI) Verification IP?

Open LVDS Display Interface (OpenLDI) Verification IP is a Single-Protocol PHY IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.