LVDS Verification IP

The LVDS Verification IP provides an effective & efficient way to verify the LPC components of an IP or SoC.

Overview

The LVDS Verification IP provides an effective & efficient way to verify the LPC components of an IP or SoC. The LVDS VIP is fully compliant with LVDS Specification, The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

Key features

- Compliant with LVDS Atmel-42415-WIRELESS-AT86RF215_ Datasheet specification.

- Supports dual independent RFIC and respective BBIC.

- Supports serial I/Q LVDS interface.

- Supports SPI control interface.

- Supports both Baseband and I/Q radio mode.

- Supports all kind of interrupts.

- Supports TX/RX frame buffering.

- Supports MR-FSK, MR-OFDM, O-QPSK.

- Supports Callbacks for error injections.

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing, and protocol violations.

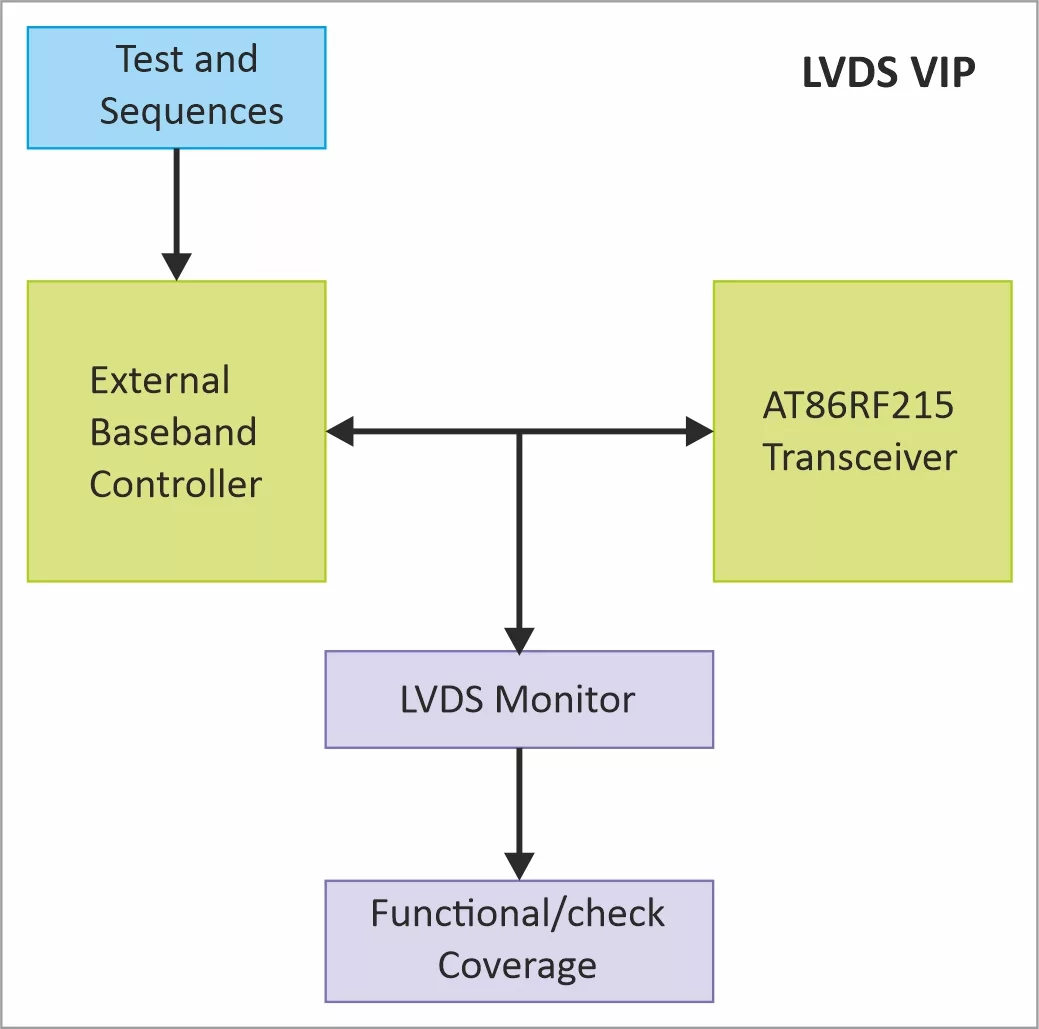

- In-built coverage analysis Test and Sequences LVDS VIP External Baseband Controller AT86RF215 Transceiver LVDS Monitor Func onal/check Coverage.

- LVDS VIP comes with a complete test suite to verify every feature.

- LVDS VIP comes with a Transaction analyser and Performance Monitors.

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure the highest levels of quality.

- Availability of various Regression Test Suites.

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

What’s Included?

- LVDS Transceivers/BFM/Agent

- LVDS Monitor ISO 9001:2015 Certified

- LVDS Scoreboard

- Testbench Configuration

- Test Suit (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertion & Cover Point Tests

- Integration Guide, User Manual and Release Notes

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is LVDS Verification IP?

LVDS Verification IP is a Single-Protocol PHY IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.