LVDS Verification IP

The SmartDV's LVDS verifies the Radio Front end-Baseband digital parallel interface.LVDS Verification IP can be used to verify BB…

Overview

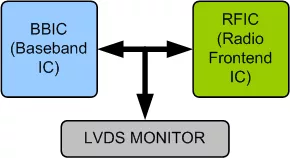

The SmartDV's LVDS verifies the Radio Front end-Baseband digital parallel interface.LVDS Verification IP can be used to verify BBIC or RFIC and SPI Master or Slave following the LVDS basic protocol as defined in LVDS and provides the following features.

LVDS Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

LVDS Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Follows LVDS Atmel-42415-WIRELESS-AT86RF215_Datasheet specification.

- Supports BBIC and RFIC Mode.

- Supports half duplex data transfer.

- Supports both data path transaction and SPI control interface transactions.

- Supports following IQ data path transaction

- Supports TXD, RXD09 and RXD24.

- Supports 2bit I SYNC and Q SYNC data.

- Supports 14bit I data and Q data

- Support error injection

- Supports following SPI control interface transaction

- 2bit command plus 14bit address and 8bit data control field format

- plane power consumption to negligible levels

- Support Master and Slave Mode

- Support baud rate selection

- Support single and burst transfer mode

- Supports various kinds of errors as follows

- I SYNC error

- Q SYNC error

- Invalid zero word error

- Illegal write data error

- Read only address error

- Status counters for various events on bus.

- Built in functional coverage analysis.

- Callbacks in BBIC and RFIC for various events.

- Functional coverage to cover each and every feature of the LVDS specification.

- Test suite to test each and every feature of LVDS specification.

Block Diagram

Benefits

- Faster test bench development and more complete verification of LVDS designs.

- Simplifies results analysis.

- Runs in every major simulation environment.

- Easy to use command interface simplifies testbench control and configuration of BBIC and RFIC.

- Comes with complete test suite to test each and every feature of LVDS.

What’s Included?

- Complete regression suite containing all the LVDS testcases.

- Examples showing how to connect various components,and usage of BBIC,RFIC and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is LVDS Verification IP?

LVDS Verification IP is a Single-Protocol PHY IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.