USB 2.0 PHY

Proven PHY IP for USB Device, Host, and OTG with small footprint and low active power Architected to quickly and easily integrate…

Overview

Proven PHY IP for USB Device, Host, and OTG with small footprint and low active power

Architected to quickly and easily integrate into any SoC, the Cadence® USB 2.0 On-The-Go (OTG) PHY IP connects seamlessly to a Cadence or third-party UTMI-compliant controller. The IP provides you with a cost-effective, low-power solution for demanding applications. It offers SoC integrators the advanced capabilities and support that exceed the requirements of high-performance designs and implementations. The Cadence USB 2.0 OTG IP is silicon-proven and has been extensively validated with multiple hardware platforms.

Key features

- Designed to the USB 2.0 specification, and operates at High Speed (480Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps)

- Complies with the UTMI v1.05 specification

- Multiple reference clock supported from 9.6MHz up to 52MHz

- 8-bit 60MHz and 16-bit 30MHz parallel interfaces

- Battery Charging Specification v1.2

- Supports link power management (LPM)

- APB and JTAG interface

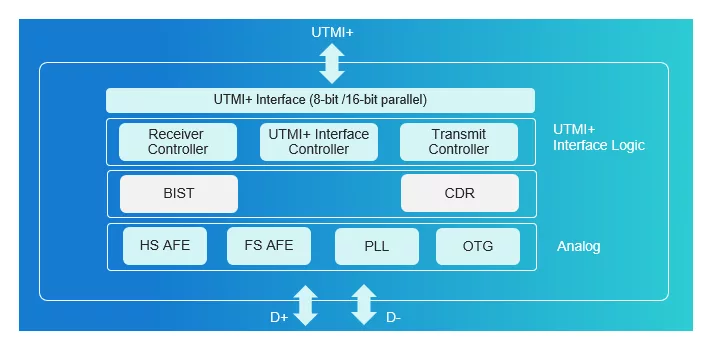

Block Diagram

Applications

- Automotive,

- Communications,

- Consumer Electronics,

- Data Processing,

- Industrial and Medical,

- Military/Civil Aerospace,

- Others

What’s Included?

- Verilog behavioral modules for PHY module

- Verilog testbench with configuration files and sample tests

- Liberty timing model

- Layout abstract in LEF format

- GDSII with flat netlist for LVS

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 7nm | N7+ | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB 2.0 PHY?

USB 2.0 PHY is a Single-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.