USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI

The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification.

Overview

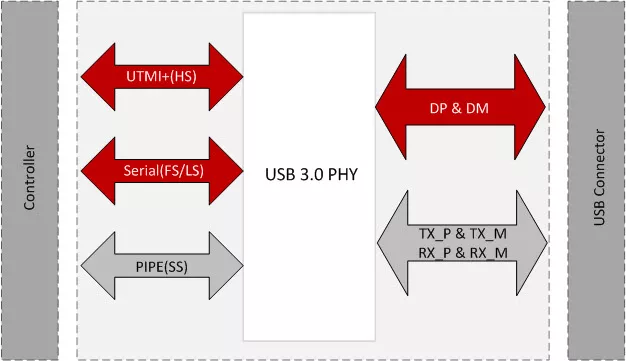

The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification. It supports the USB3.0 5Gbps Super-Speed mode and backward compatibles with the USB2.0 480Mbps High-Speed, 12Mbps Full-Speed, and 1.5Mbps Low-Speed modes. The USB 3.0 PHY interface complies with PHY Interface for PCI Express and USB3.0 Architectures specification (PIPE 3.0) and the USB2.0 PHY interface complies with the UTMI v1.05 specification.

Implemented on the GF22FDX and Samsung 28nm FDSOI process, the USB3.0 PHY IP provides a cost-effective, low-power solution for demanding applications.

Key features

- Silicon proven in 22, 28, Global Foundries and Samsung

- Spread Spectrum clock (SSC) and data scrambling to minimize EMI

- Supports 16-bit 250-MHz , and 32-bit 125M PIPE interface

- Multiple loopback and compliance test modes

- On chip Eye Opening Monitor (EOM) to measure the eye diagram at the receiver side

- PIPE 3-compliant Super-Speed USB 3.0 Transceiver interface

- 5-Gbps Super-Speed data transmission rate through 3-m USB3.0 cable

- Supports Super-Speed power management modes: U0, U1, U2 and U3

- Built-in BIST pattern generator and checker with programmable modes for stand-alone tests

- -3.5dB de-emphasis at the TX side and programmable CTLE equalization at RX side

- IEEE standards 1149.1 and 1149.6(JTAG) boundary scan for internal visibility and control

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| Samsung | 28nm | FDS | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI?

USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI is a Single-Protocol PHY IP core from VeriSilicon Microelectronics (Shanghai) Co., Ltd. listed on Semi IP Hub. It is listed with support for samsung Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.