Home Plug Green PHY MAC Layer TX/RX

ntHPGP_MAC IP core implements “Connectionless CSMA-Only Level-0 CCo“ MAC Layer functionality with Passive Coordination, as detail…

Overview

ntHPGP_MAC IP core implements “Connectionless CSMA-Only Level-0 CCo“ MAC Layer functionality with Passive Coordination, as detailed in Chapter 5 of “HomePlug Green PHY 1.1.1” (HPGP) specification document.

The MAC Layer is positioned in the middle of the HPGP Protocol Layer Architecture and it manages communication and transactions between all surrounding HPGP Layers.

Namely it is connected to the Connection Manager (CCo) via the Control SAP IF ports, to the Convergence Layer via the M1 SAP IF ports and to the PHY Layer via the MAC-PHY SAP IP ports.

All these 3 Service Access Points (SAP) are loosely defined in the specification document. The MAC is also tasked to determine the correct time position of transmission, format data frames into fixed length entities and ensure

timely and error-free delivery.

ntHPGP_MAC IP defines customizable interfaces and optional interrupt ports for all 3 SAP ports and implements specific detailed packet and timing protocols for the communication with all adjacent HPGP Protocol layers.

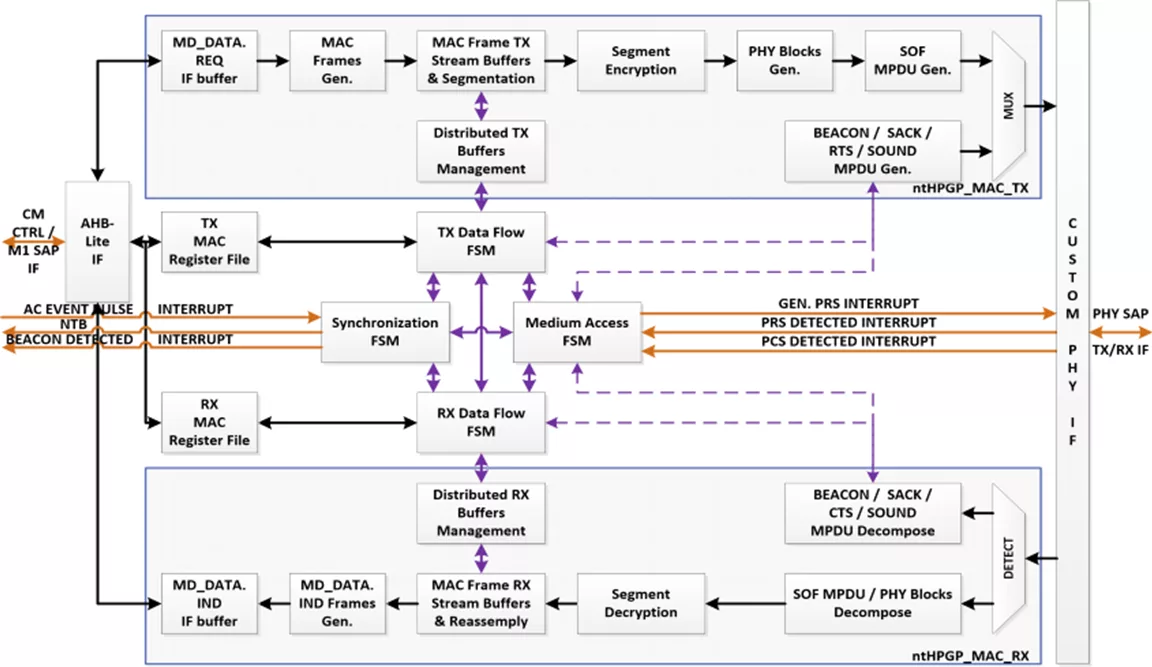

The implementation is further partitioned to the Control Plane and the Data Plane. The Control plane is implemented with a number of coordinated and distributed FSM controllers, each managing a standalone MAC Layer system task.

A set of Synchronization FSMs manage the AC Line Synchronization, the Network Time Base (NTB) Synchronization and the Beacon Period Tracking. A set of Medium Access FSMs both implement and manage the CSMA/CA medium access protocol, implement the Virtual Carrier Sense (VCS) mechanism and ultimately cooperate with Synchronization FSMs to indicate appropriate Transmit and Receive periods to the system.

The TX and RX data-flow FSMs make timely decisions regarding the types of MPDU frames that need to be transmitted or effectively detect the received MPDU frames.

The Data plane is implemented with the TX and RX data-path IPs. The TX IP accepts MD_DATA.REQ primitives and ultimately converts MSDU/MME payload to SOF MPDU Frames.

This procedure involves conversion of MSDU/MME to MAC Frames, segregation of MAC Frames to MAC Frame Streams, segmentation, encryption, formation of Payload Blocks and finally SOF MPDU Frames generation.

The inverse procedure is implemented by the RX IP, which accepts MDPU Frames and converts them back to MD_DATA.IND primitives.

Key features

- CCo-Level 0 CSMA-Only Connectionless HPGP MAC Layer subset.

- AC Line synchronization algorithm with failsafe provisions for AC loss.

- Network Time Base synchronization algorithm on received Beacon Headers with failsafe provisions for Beacon loss.

- Channel State Synchronization with CSMA/CA, VCS, PHY PCS and RX detection filter module.

- Distributed controller design with fine tuned selective resetting capabilities, in order to avoid dead-lock on unexpected system conditions.

- Hybrid Mode / AV-Only mode selection.

- CCo / STA mode selection.

- CSMA/Stay-out Regions Allocation scheduling via relative Beacon

- BENTRY fields.

- Distributed Bandwidth Control (DBC) mechanism implementation.

- Power Save Schedule feature implementation.

- Partial ARQ and Multiple Networks mechanisms support.

- 1.0.1 Networks basic coexistence awareness via Hybrid

- Delimiters management is supported.

- Parametric (pre-synthesis) implementation of individual TX and RX stream buffers instances number [MAX_STR_NUM = 4 8 16 32].

- Parametric (pre-synthesis) implementation of each stream buffer instance depth measured in number of 512byte

- segments [SB_SIZE = 4 8 16 32].

- Dynamic self managed controller used to commit and release TX/RX stream buffers automatically, based on detected traffic, for optimum data-flow and resources allocation.

- Low power 25 MHz clock design. Additional clock synchronization circuits to/from PHY layer (75 MHz) clock domain.

Block Diagram

Benefits

- Smart-grid charging.

- Compliant with HPGP and HPAV standards.

Applications

- EV charging.

What’s Included?

- Fully commented synthesizable VHDL/Verilog source code or FPGA netlist.

- VHDL/Verilog test bench and example configuration files.

- Comprehensive technical documentation.

- Technical support.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Home Plug Green PHY MAC Layer TX/RX?

Home Plug Green PHY MAC Layer TX/RX is a Single-Protocol PHY IP core from Noesis Technologies listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.