Simulation VIP for eMMC

In production since 2011 on dozens of designs.This Cadence® Verification IP (VIP) supports the JEDEC® eMMC standard.

Overview

In production since 2011 on dozens of designs.

This Cadence® Verification IP (VIP) supports the JEDEC® eMMC standard. The eMMC standard is an industry-leading memory standard for embedded non-volatile storage of system code, software applications and user data. The JEDEC eMMC 5.1 standard defines functionality that focuses on improving the interaction between the host processor and the memory device at the interface, configuration and protocol levels, resulting in potential gains in overall system performance and reliability. The eMMC VIP is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: JEDEC eMMC Electrical Standard, Version 4.51 (JESD84-B451), JEDEC eMMC Electrical Standard, Version 5.0, (JESD84-B50) and JEDEC eMMC Electrical Standard, Version 5.1 (JESD84-B51)

Key features

- High speed modes

- 200 MB/s Read and Write operation. HS400 Dual Data Rate Read and Write interface

- General eMMC Functionality

- 48-bit input command format and R1, R1b, R2 response formats

- CID/CSD/OCR/Ext_CSD registers bit definitions for a subset of eMMC standard bit definitions

- Voltage range negotiation through CMD1

- Cache Read/Write operations, Context ID Management functionality, Discard operation, Packed Read and Write operation, Sanitize operation

- Read and Write operations for large 4Kb sector sizes

- Command queuing feature

- Data tag mechanism

- Enhanced strobe in HS400 mode with "Data Strobe" signal which directs bit transfer on data lines

- Extended Partition Types operation

- DDR Timing

- Supports Dual Data Rate timing mode for Read/Write operations, reading CID and CSD registers, sending CRC status and Boot acknowledge

- Address Mechanism

- For devices larger than 2GB, the addressing mechanism is switched from byte addressing to sector addressing

- Memory Block Protection

- Support Replay Protected Memory Block functionality and Secure Write protection feature with Authenticated Device Configuration Area

- Interrupt

- High Priority Interrupt mechanism

- Power Off Notification

- Notification mechanism when the host intends to power off the device

- Real Time Clock

- Accepting Real Time Clock Information that the host sends to the card

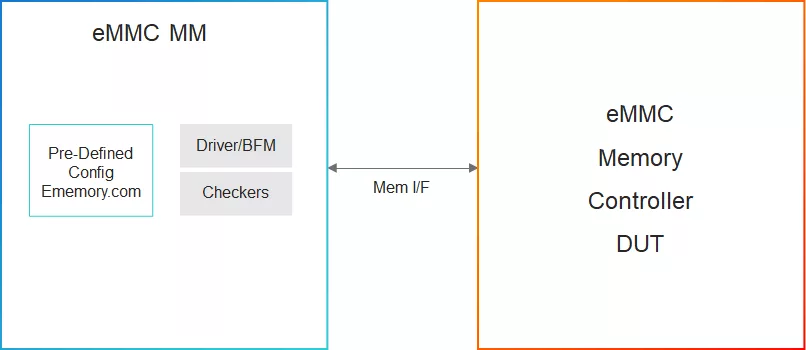

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is Simulation VIP for eMMC?

Simulation VIP for eMMC is a SD / eMMC Controller IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.