SDIO UHS II Verification IP

SDIO UHS II Verification IP is an solution in the market for the verification of SDIO UHS-II implementations.It can generate all …

Overview

SDIO UHS II Verification IP is an advanced solution in the market for the verification of SDIO UHS-II implementations.It can generate all command types. The SDIO UHS-II monitor acts as powerful protocol-checker, fully compliant with UHS-II Adddendum version 2.00.

SDIO UHS-II VIP includes an extensive test suite covering most of the possible scenarios and SDIO UHS-II conformance norms. SDIO UHS-II VIP can perform all protocol tests as testbench and moreover it allows an easy generation of a very high number of patterns and a set of specified patterns to stress the DUT.

SDIO UHS II Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SDIO UHS II Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports SD specification UHS-II Adddendum version 2.00 compliant.

- Supports Part E1 SDIO specification version 4.10.

- Supports SD specification physical layer version 4.0/4.20/5.0/5.10/6.0/6.10/7.0/7.10/8.0(Draft).

- Supports bi-directional receiver/transmitter (2ch) supporting both Full Duplex and Half Duplex modes.

- Supports PHY-LINK interface.

- Supports lock-unlock and erase operation card features.

- Supports point-to-point and Ring connection.

- Supports RCLK frequency: 26~56MHz.

- Supports higher bus speed of UHS II(UHS III).

- Supports high speed interface up to 312MB/s for Version 1.02, and up to 624MB/s for Version 2.00.

- Supports Full Duplex mode (FD mode): data rate from 39MB/sec to 156MB/sec in Version 1.02. The maximum speed of this mode is enhanced to 624MB/s in Version 2.00.

- Supports Half Duplex with 2 Lanes mode (2L-HD mode): data rate from 78MB/sec to 312MB/sec in Range A and Range B.

- Supports following additional lanes features

- Full Duplex with 2 Downstream and 1 Upstream Lanes mode

- Full Duplex with 1 Downstream and 2 Upstream Lanes mode

- Full Duplex with 2 Downstream and 2 Upstream Lanes mode

- Single byte, single block, multiple block (finite and infinite) transfers and MMC stream transfer operations.

- Supports Bus-accurate timing.

- Supports fast mode and low power mode.

- Supports video class specification.

- Supports flow control operations.

- Supports Function extension commands.

- Supports test modes.

- Supports hibernate mode.

- Supports enumeration.

- Supports power saving modes.

- Supports 8b10b encoding/decoding.

- Supports clock phase adjustment.

- Supports serializer and de- serializer(SERDES).

- Supports data transaction for SD-TRAN and CM-TRAN.

- Supports data transaction transfer length is fixed and infinite for SD-TRAN and CM-TRAN.

- Supports card ownership protection.

- Supports discard and Full user area logical erase.

- Supports cache operation.

- Supports command queuing.

- Supports Card maintenance (background operations).

- Supports Low voltage 1.8V cards.

- Detects and reports the following errors.

- Out of range error

- Address misalign error

- CRC error

- Switch error

- Illegal command error

- Block length error

- Lock-unlock failed error

- Erase sequence error

- Stuff bit error

- Invalid voltage error

- Reserved bit error

- WP violation error

- CSD/CID over write error

- Disparity error insertion

- Invalid K character error

- Missing K character error

- Link layer error injection

- Initialization error injection

- Illegal header error

- Device specific error

- Retry expiry error

- Frame error

- Scrambler error

- Protocol Checker fully compliant with SDIO specification 4.10, SD specification physical layer specification 4.0/4.20/5.0/5.10/6.0/6.10/7.0/7.10/8.0(Draft) and UHS-II Addendum version 2.00 compliant.

- SDIO UHS Verification IP comes with complete testsuite to test every feature of SDIO UHS specification.

- Monitors, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- Status counters for various events on bus.

- Functional coverage for complete SDIO UHS-II features.

- Monitors, detects and notifies the testbench of all protocol and timing violations.

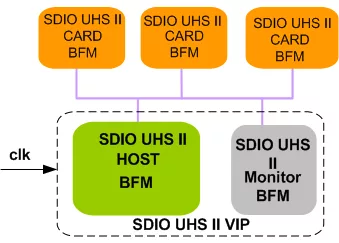

Block Diagram

Benefits

- Faster testbench development and more complete verification of SDIO UHS-II designs.

- Easy to use command interface simplifies testbench control and configuration of slave and host.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SDIO UHS-II testcases.

- Examples showing how to connect various components, and usage of Host, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is SDIO UHS II Verification IP?

SDIO UHS II Verification IP is a SD / eMMC Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.