eMMC v5.1/A Verification IP

The eMMC 5.1/A verification IP provides an effective and efficient way to verify the component interfacing with the eMMC interfac…

Overview

The eMMC 5.1/A verification IP provides an effective and efficient way to verify the component interfacing with the eMMC interface of an ASIC / FPGA / SoC. The eMMC verification IP fully complies with standard eMMC versions JESD84-B51 and JESD84-B51A from JEDEC. This VIP is a Light Weight VIP with easy plug-and-play features.

Key features

- Compliant with JEDEC eMMC version JESD84 - B51 and JESD84 – B51A.

- Supports eMMC devices from all leading vendors.

- Supports configuration for both host and device.

- Support all data widths 1x, 4x, and 8x.

- Supports all speed modes ( Legacy Speed Mode and High-Speed Mode ).

- Support both Single Block and Multiple Block transfers.

- Supports Tuning.

- Supports general-purpose commands.

- Supports Lock / Unlock feature.

- Supports Block Read and Block Write.

- Supports device density Greater than or equal to 2GB ( Low Capacity and High Capacity ).

- Supports both Normal Booting and Alternate Boot operation.

- Supports Sleep Mode and Sleep Notification.

- Supports Reliable Write feature.

- Supports Write Protection Mechanism.

- Supports Multiple Partitions ( Boot Area / User Area / General Purpose Partition ).

- Supports Enhanced Partition Types.

- Support for both SDR and DDR.

- Supports Data Removal Commands Erase ( High Capacity ) / Trim / Sanitize / Discard.

- Supports Secure Erase/TRIM.

- Strong protocol monitor with a real-time exhaustive programmable check.

- Supports Dynamic as well as static error injection scenarios.

- Built in coverage analysis.

- Graphical analyzer to show transactions for easy debugging.

- Provides a comprehensive user API (callbacks) in all components and BFMs

- Provide an Intention check for all the scenarios.

- Supports all the setup/hold timing parameter checks compliant with the eMMC specification.

- Supports Replay Protect Memory Block ( RPMB ).

- Supports Background Operations.

- Supports High Priority Interrupt.

- Supports boot partition, boot operation, and boot partition write protection.

- Supports device reset to pre-idle state.

- Supports Secure Erase and Secure Trim.

- Supports Sleep and Awake.

- Supports Secure Write Protect Mode.

- Supports Command Queuing.

- Supports Enhanced Strobe in HS400 Mode.

- Supports High-Speed Mode ( HS200, HS400 ).

- Supports Application-Specific commands.

- Supports Context Management.

- Supports Data Tag Mechanism.

- Supports Packed Commands.

- Supports Dynamic Capacity Management.

- Supports Power Off Notifications and Packed Commands.

- Supports Extended Security Commands.

- Supports Power Saving Mode.

- Supports Field Firmware Update.

- Supports Real Time Clock.

- Supports all Device Statuses ( Switch Error, CSD/CID Error, Block Length Error, etc ).

- Supports Cache ( Including Barrier and Flush Operation ).

- Supports Production State Awareness.

- Supports Hardware Resets and Software Reset ( CMD0 ).

- Supports Sector Memory Organisation.

- Supports all timing delay ranges.

- Reports various timing errors, which can be used to check any timing violation.

- Provides full control to the user to enable/disable various types of messages.

- Supports advanced System Verilog features like constrained random testing.

- Supports dynamically configurable modes.

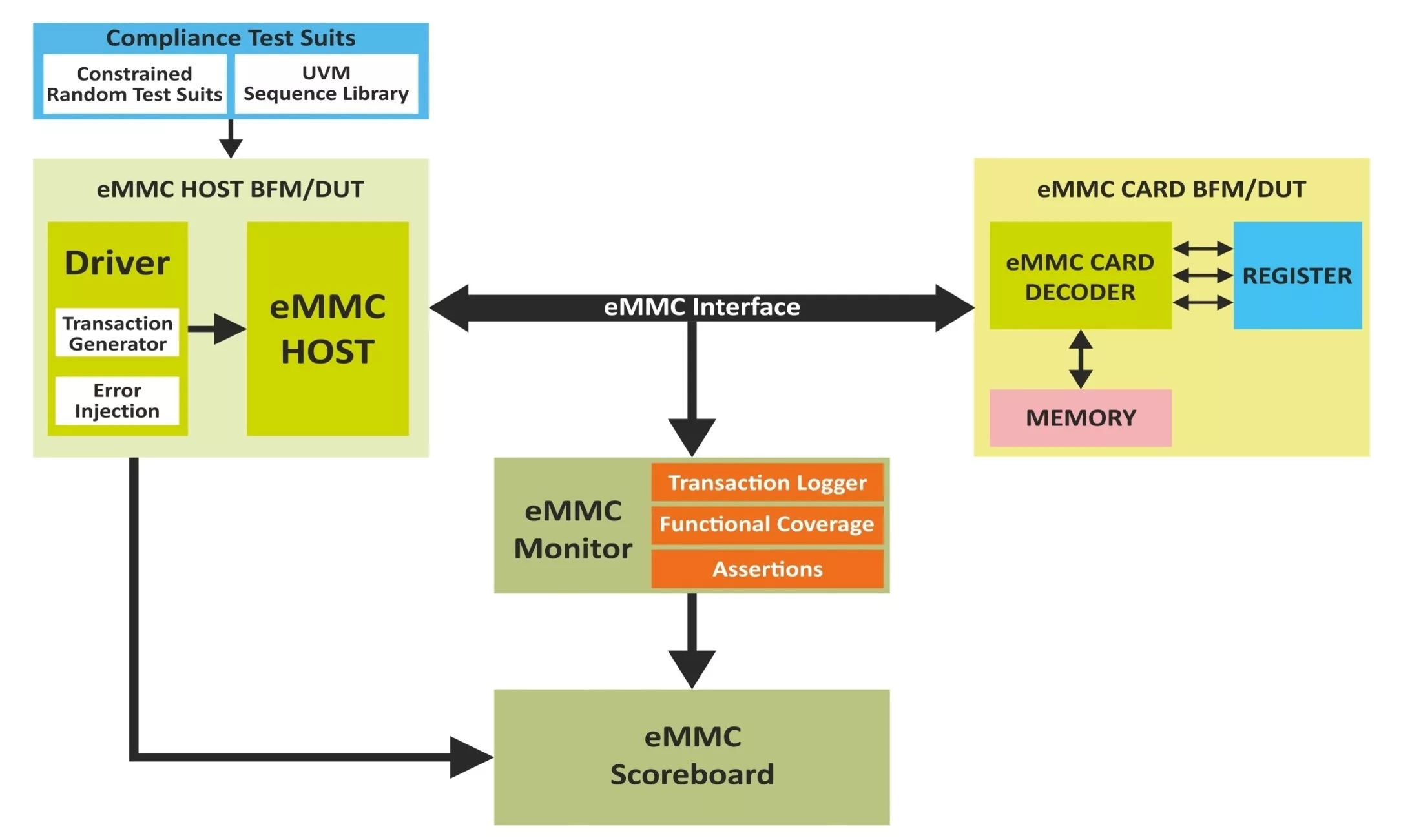

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

What’s Included?

- eMMC Host controller BFM / Agent

- eMMC Device Controller / Memory BFM / DUT

- eMMC Monitor

- eMMC Scoreboard

- Test Bench Configurations

- Test suite available in source code:

- Basic Protocol Tests

- Directed and random test

- Assertions & Cover Point Tests

- Integration guide / User Manual /release notes

- GUI analyzer to view simulation packet flow

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is eMMC v5.1/A Verification IP?

eMMC v5.1/A Verification IP is a SD / eMMC Controller IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.