eMMC Synthesizable Transactor

eMMC Synthesizable Transactor is an solution in the market for the verification of eMMC implementations.

Overview

eMMC Synthesizable Transactor is an advanced solution in the market for the verification of eMMC implementations. eMMC is build on top of it to make it robust. eMMC Synthesizable Transactor provides a smart way to verify the eMMC component of a SOC or a ASIC in Emulator or FPGA platform. It is adherent with eMMC standard JESD84-A441, JESD84-B45,JESD84-B50 & JESD84-B51. It can generate all command types. eMMC JESD84-A441, JESD84-B45,JESD84-B50 & JESD84-B51 VIP can perform all protocol tests as testbench and moreover it allows an easy generation of a very high number of patterns and a set of specified patterns to stress the DUT. eMMC Synthesizable Transactor provides a smart way to verify the UART component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's eMMC Synthesizable Transactor is fully compliant with standard UART 16550 Specification and provides the following features.

Key features

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

- 4-bit

- 8-bit

- Supports boot operation mode with simple boot sequence method.

- Supports alternative boot operation mode.

- Supports higher than 2GB of density of memories.

- Supports hardware reset signal.

- Supports high speed boot operation.

- Supports command queuing.

- Supports enhanced strobe.

- Supports extended security protocols commands.

- Supports production state awareness.

- Supports secure write protect mode.

- Supports Replay Protected Memory Block(RPMB) functionality.

- Supports Single byte, single block, multiple block (finite and infinite) transfers and MMC stream transfer operations.

- Supports send tuning block(CMD21) command.

- Supports HS200 and HS400 Mode.

- Supports data protection mechanism like password, permanent ,power-on and temporary.

- Supports data removable mechanism.

- Supports packed commands.

- Supports high voltage & dual voltage.

- Supports single data rate & dual data rate.

- Supports write protection features for the boot and user areas, which may be permanent, power-on or temporary.

- Tracking of transmit and receive counters.

- Supports bus accurate timing.

- Detects and reports the following errors.

- Out of range error

- Address misalign error

- CRC error

- Switch error

- Illegal command error

- Block length error

- Lock-unlock failed error

- Erase sequence error

- Direction bit error

- Stuff bit error

- Erase param error

- Reserved bit error

- WP violation error

- CSD/CID over write error

- Protocol Checker fully compliant with eMMC JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A Specification.

- Supports constraints randomization.

- eMMC Verification IP comes with complete testsuite to test every feature of JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A.

- Status counters for various events on bus.

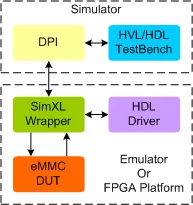

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the eMMC testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is eMMC Synthesizable Transactor?

eMMC Synthesizable Transactor is a SD / eMMC Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.