Simulation VIP for AMBA CHI

Best-in-class Arm® AMBA® CHI Verification IP (VIP) for your IP, SoC, and System-level Design Testing Cadence provides a mature an…

Overview

Best-in-class Arm® AMBA® CHI Verification IP (VIP) for your IP, SoC, and System-level Design Testing

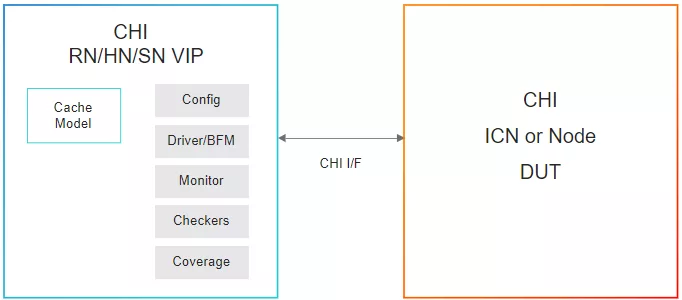

Cadence provides a mature and comprehensive Verification IP (VIP) for the Coherent Hub Interface (CHI) specification, which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence Verification IP for CHI provides a complete bus functional model (BFM), integrated automatic protocol checks, and a coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for CHI provides a highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms. Cadence provides an integrated solution for interconnect verification, which supports the verification of coherent interconnect and performance analysis that provides automated generation of testbenches. The VIP runs on all major simulators and supports SystemVerilog and e verification languages, along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Key Features

The table below shows the key features from the specifications implemented in the VIP:

| Feature Name | Description |

|---|---|

| Transaction type |

|

| Dummy interconnect |

|

| Communication layers |

|

| Interface |

|

| Flow control |

|

| Channel delay |

|

| Cache model |

|

| Cache access |

|

| CHI-B |

|

| CHI-C |

|

| CHI-D |

|

| CHI-E |

|

| CHI-F |

|

| CHI-G |

|

| CHI-H |

|

| Waveform Debugger |

|

Support Specification

- AMBA 5 CHI A, B, C, D, E, F, G and H

Block Diagram

Benefits

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection

- Callbacks access at multiple queue points for scoreboarding and data manipulation

- Provides comprehensive checking and coverage model

- Includes embedded memory model in SN models

- Includes embedded cache model in RN-F models

- Packet tracker for ease of debugging

- Seamless integration with System Verification Scoreboard (SVD) and System Performance Analyzer (SPA)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Coherency IP core

CCIX Coherency: Verification Challenges and Approaches

Cache Coherency Is the New Normal

Increased CHI Coherency Verification Challenges

Fast, Thorough Verification of Multiprocessor SoC Cache Coherency

Co-Designed Cache Coherency Architecture for Embedded Multicore Systems

Frequently asked questions about Coherency Interconnect IP cores

What is Simulation VIP for AMBA CHI?

Simulation VIP for AMBA CHI is a Coherency IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Coherency?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Coherency IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.