Verification IP for Arm AMBA CHI Protocol

Synopsys Verification IP (VIP) for Arm® AMBA® CHI provides a comprehensive set of protocol, methodology, verification and product…

Overview

Synopsys Verification IP (VIP) for Arm® AMBA® CHI provides a comprehensive set of protocol, methodology, verification and productivity features, enabling users to achieve accelerated verification closure of Issue A/B/C/D/E/F/G based interconnects and interfaces. AMBA CHI VIP works in conjunction with other Synopsys AMBA VIP to provide a complete system solution for AMBA based designs.

AMBA CHI Verification

System Environment

The Synopsys CHI VIP simulates CHI transactions through active agents, as defined by the CHI specification. The VIP provides a CHI System Environment (Env) which comprises of agents for RN (Request Node) and SN (Secondary Node), and a CHI System Monitor. The RN and SN agents support all the protocol features as per the CHI Specification and the methodology functionality normally associated with active and passive UVM components. The RN agent has an internal cache model which facilitates the sole of actual cache and the SN agent has an inbuilt memory instance.

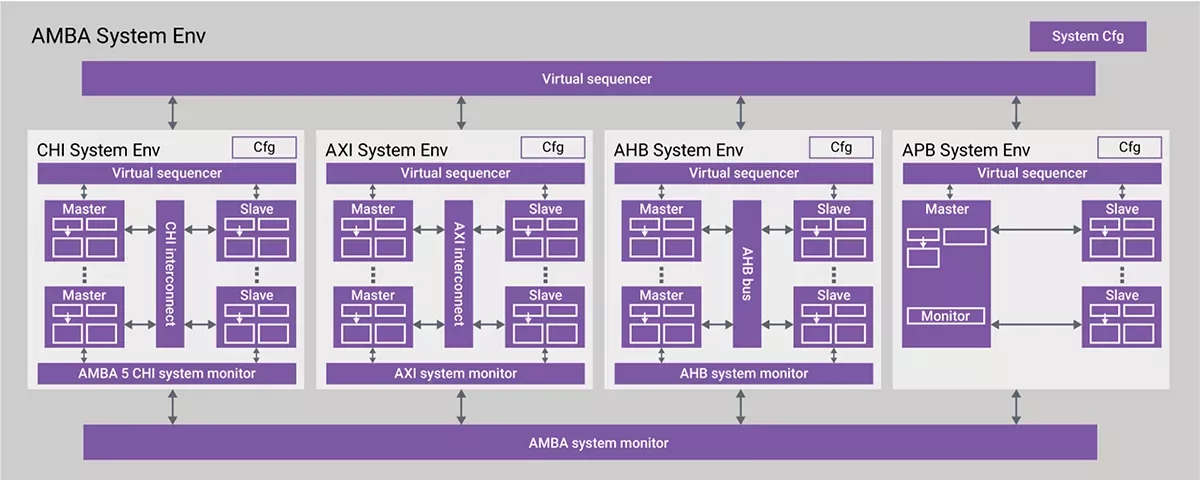

The CHI System Environment itself is contained within top level System VIP component AMBA System Environment. UserS can either use AMBA System Env, CHI System Env, or standalone RN and SN agents in the testbench. The CHI System Monitor component is instantiated within the CHI System Env component. The System Monitor performs system-level checks across the CHI RN and SN ports within the system to ensure coherency is maintained as per the protocol.

AMBA Verification System Environment

The AMBA CHI verification system environment is integrated with the AMBA verification system environment to provide all of the configurability of the AMBA CHI Verification System Environment with the addition of AMBA 4 AXI, ACE, AHB and APB verification system environments. A system monitor provides system-wide checking across all of the protocols.

Key features

- AMBA 5 CHI-A/B/C/D/E/F/G

- Request node, secondary node agents and monitor

- Complete port-level checks

- Supports all interface types

- AMBA CHI system monitor provides system-wide coherency and data integrity checks

- AMBA CHI system environment encapsulates CHI primariy, secondary, monitors, interconnect environment

- AMBA system environment encapsulates CHI and other AMBA protocols

- VC SoC AutoTestBench helps in improving productivity by automatically generating SV UVM testbench reading DUT information

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Coherency IP core

CCIX Coherency: Verification Challenges and Approaches

Cache Coherency Is the New Normal

Increased CHI Coherency Verification Challenges

Fast, Thorough Verification of Multiprocessor SoC Cache Coherency

Co-Designed Cache Coherency Architecture for Embedded Multicore Systems

Frequently asked questions about Coherency Interconnect IP cores

What is Verification IP for Arm AMBA CHI Protocol?

Verification IP for Arm AMBA CHI Protocol is a Coherency IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Coherency?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Coherency IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.