Verification IP for Arm AMBA ACE Protocol

Synopsys Verification IP (VIP) for Arm® AMBA® ACE provides a comprehensive set of protocol, methodology, verification, and produc…

Overview

Synopsys Verification IP (VIP) for Arm® AMBA® ACE provides a comprehensive set of protocol, methodology, verification, and productivity features, enabling users to achieve accelerated verification closure of Arm AMBA-based designs supporting AMBA ACE 5, H, J and K, ACE4, ACE-Lite, AXI5, AXI4, AXI4-Lite, and AXI3.

Key features

- Complete protocol support for AMBA ACE 5, H, J and K, ACE4, ACE-Lite, AXI5, AXI4, AXI4-Lite, and AXI3.

- Configurable interconnect model for AXI5, AXI4, AXI, ACE5, and ACE4

- Backdoor access to ACE primary cache

- Ability to control delays for valid and ready signals with respect to reference events

- Ability to control signal values during idle periods

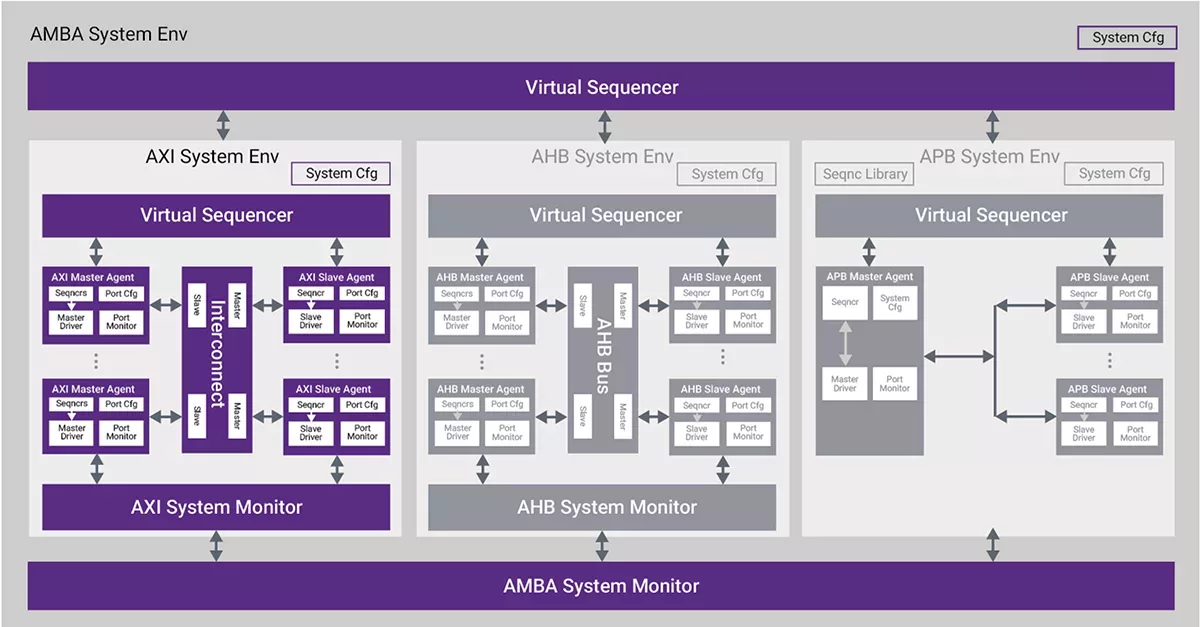

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Coherency IP core

CCIX Coherency: Verification Challenges and Approaches

Cache Coherency Is the New Normal

Increased CHI Coherency Verification Challenges

Fast, Thorough Verification of Multiprocessor SoC Cache Coherency

Co-Designed Cache Coherency Architecture for Embedded Multicore Systems

Frequently asked questions about Coherency Interconnect IP cores

What is Verification IP for Arm AMBA ACE Protocol?

Verification IP for Arm AMBA ACE Protocol is a Coherency IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Coherency?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Coherency IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.