Simulation VIP for AMBA ACE

Cadence provides a mature and comprehensive Verification IP (VIP) for the ACE specification which is part of the Arm® AMBA® famil…

Overview

Cadence provides a mature and comprehensive Verification IP (VIP) for the ACE specification which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence® Verification IP for ACE provides a framework for system-level coherency, integrated automatic protocol checks, and coverage model. Cadence provides an integrated solution for interconnect verification that supports the verification of coherent interconnect and performance analysis that provides automated generation of testbenches. The VIP provides a mature, highly capable compliance verification solution making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for AMBA ACE is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported specification: AMBA ACE-Lite, AMBA 5 ACE, AMBA 5 ACE-Lite, AMBA 5 ACE-LiteDVM interfacesת AMBA ACE issues F, G, and H.

Key features

- ACE-Lite

- Support for ACE-Lite configuration; automatically modify the agent accordingly

- Data and Address Widths

- Supports all legal data and address widths

- Multiple Agents

- Supports any number of agents

- Automatic Subordinate Responses

- Support for automatic Subordinate responses

- Barrier Transactions

- Supports monitoring and driving of barrier transactions

- Cache Model

- Cache model in both active and passive manager agents including cache state checks

- Transmission Order Control

- Support for control over the order of transmission of read transfers and write responses

- Data Before Address

- Supports sending of data before address transactions

- Delay Control

- Sets the delay between the items on the channels

- DVM Transactions

- Supports monitoring and driving of DVM (Distributed Virtual Memory) transactions

- Exclusive Access

- Supports monitoring and driving of all exclusive transactions

- Manager Signals Control

- Support for control over the values of the burst, transfer, snoop, and snoop response signals

- Subordinate Response Control

- Support for control over the values of the signals in the read data channel

- Snoop Filter

- Supports connection to a snoop filter

- Transaction Types

- Supports monitoring and driving of all read and write transactions

- Atomic Transactions

- Supports atomic transactions

- Cache Stashing

- Support for cache stashing

- Other Signaling

- Support for Wake-up Signaling, User Loopback Signaling, QoS Accept Signaling, and Coherency Connection Signaling

- Armv8.1

- Supports Distributed Virtual Memory Extensions for Armv8.1 architecture

- Untranslated Transactions

- Support for Untranslated Transactions

- Non-Secure Access Identifiers

- Support for Non-Secure Access Identifiers

- MPAM

- Supports Memory Partitioning and Monitoring functionality

- MTE

- Supports Memory Tagging Extensions functionality

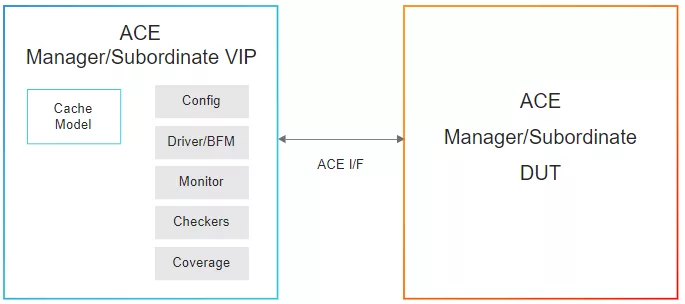

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Coherency IP core

CCIX Coherency: Verification Challenges and Approaches

Cache Coherency Is the New Normal

Increased CHI Coherency Verification Challenges

Fast, Thorough Verification of Multiprocessor SoC Cache Coherency

Co-Designed Cache Coherency Architecture for Embedded Multicore Systems

Frequently asked questions about Coherency Interconnect IP cores

What is Simulation VIP for AMBA ACE?

Simulation VIP for AMBA ACE is a Coherency IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Coherency?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Coherency IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.