RISC-V CPU IP

The TT-Ascalon™ is an Out-of-Order, superscalar, 8-wide decode processor based on the RISC-V RVA23 profile, co-designed and optim…

Overview

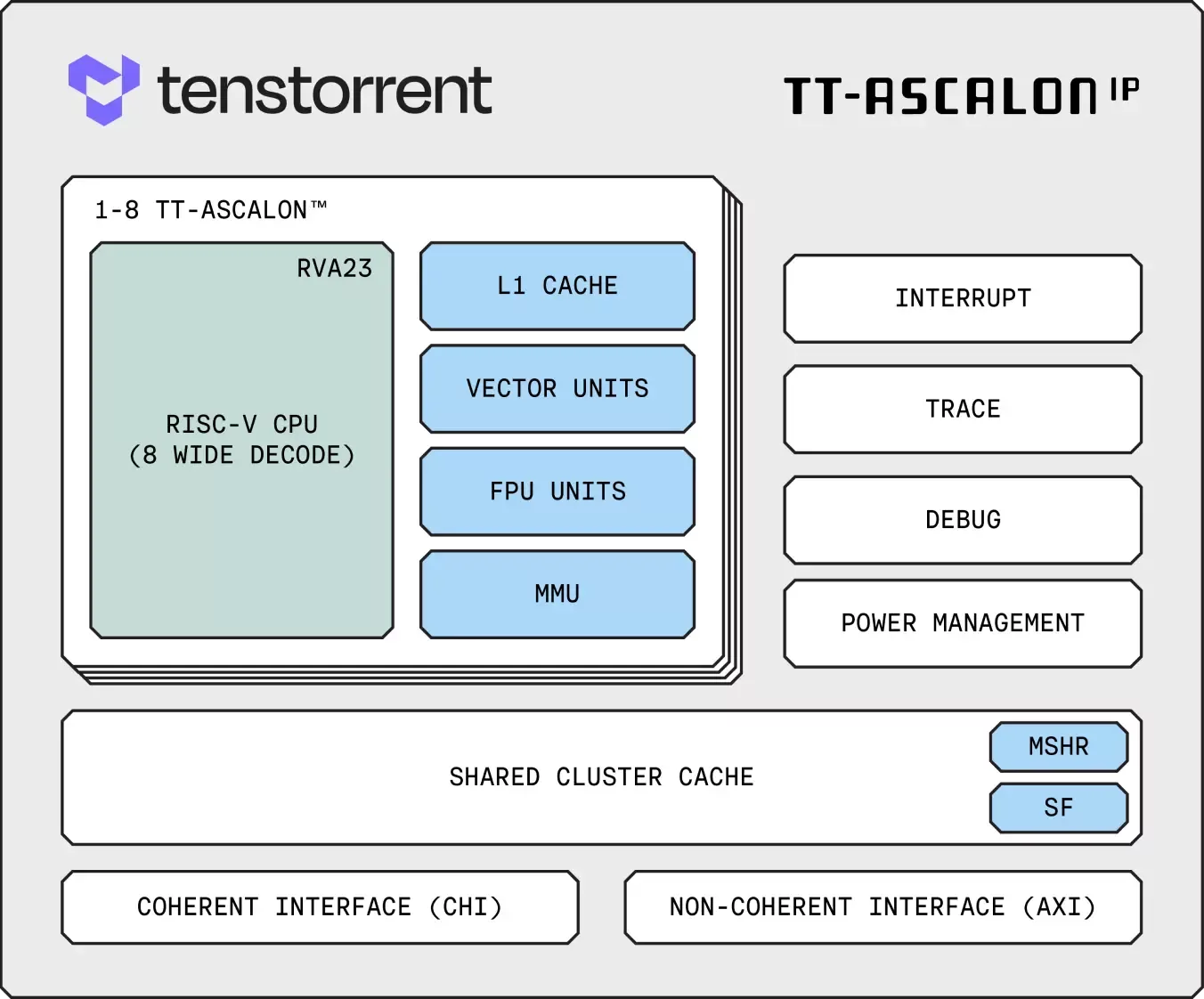

The TT-Ascalon™ is an Out-of-Order, superscalar, 8-wide decode processor based on the RISC-V RVA23 profile, co-designed and optimized with Tenstorrent Tensix IP to provide the highest performance possible (>18 SPECint2006/GHz) while maintaining area/power efficiency. TT-Ascalon™ can be combined with your IP for optimized solutions for next generation AI/ML compute and beyond. TT-Ascalon™ D8 Cores are encapsulated inside the TT-Ascalon™ Cluster, which coherently connects all Cores with shareable L2 cache and interfaces to the memory

Key features

- RISC-V RVA23 Compliant

- >18 SPECint2006/GHz

- 8-wide decode unit

- Advanced branch predictor

- Large L1 cache

- Shared configurable L2 cache

- RVV 1.0 compliant vector unit

- Dual 256b-wide vector units

- TT-Ascalon™ D8 Cluster Features

- Consists of up to 8 RISC-V RVA23 Compliant TTAscalon™ D8 Cores for maximum performance

- Configurable shared L2 cache

- Cache coherent cluster

- RISC-V compliant Advanced Interrupt Architecture (AIA)

- RISC-V compliant Trace and Debug unit

- CHI-E coherent and AXI5-LITE non-coherent interfaces

- Support for Trusted Execution Environment

Block Diagram

Benefits

- Open Source

- High Performance

- Customizable

Applications

- TT-Ascalon™ is a compute solution for High Performance Compute SoCs targeting Cloud Servers, Data Centers, Wireless Communications, Automotive ADAS/AV, and Client Computing devices. TT-Ascalon™ can be combined with your IP for building accelerated compute processors for next generation workloads.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is RISC-V CPU IP?

RISC-V CPU IP is a CPU IP core from Tenstorrent listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.