RISC-V Debug & Trace IP

10xEngineers Debug & N-Trace IP delivers a unified Debug + Trace solution that provides full-system visibility with low overhead …

Overview

10xEngineers Debug & N-Trace IP delivers a unified Debug + Trace solution that provides full-system visibility with low overhead and multi-hart awareness. Standards-compliant debug, real-time trace, and flexible triggering significantly reduce bring-up time and simplify system integration.

Why Choose 10xEngineers Debug & N-Trace IP?

The 10xEngineers Debug & N-Trace IP is designed to give engineering teams a complete, high-performance, and easy-to-integrate solution for debugging and tracing multi-core RISC-V SoCs—from early bring-up through post-silicon validation.

Key features

Debug Features

- Fully compliant with RISC-V Debug v1.0

- Hart groups with independent reset support

- Secure authentication and access control

- System Bus Access (SBA) for memory inspection

- External trigger support for advance debugging & event capture

Trace Features

- IEEE-5001 Nexus standard compliance

- Support for both BTM & HTM trace modes

- Multi hart tracing with timestamp support

- On-chip & off-chip trace storage options

- Event driven trace with configurable filters and compare units

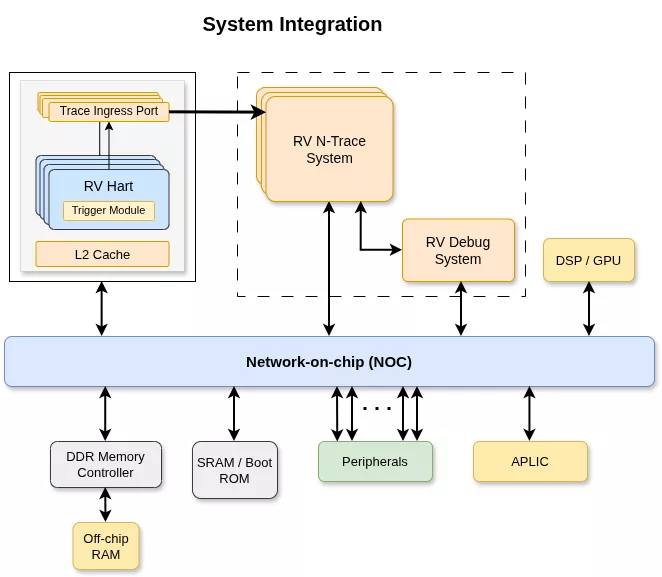

Block Diagram

Benefits

- Specification Compliance: Fully compliant with Debug Spec v1.0 and N-Trace Spec v1.0, ensuring interoperability with standard tools and workflows.

- Full Multi-Hart Visibility: Halt, step, and inspect multiple harts simultaneously for comprehensive execution insight.

- Non-Intrusive, Real-Time Trace: Capture instruction execution with minimal impact on core performance.

- Flexible Interfaces: APB and AXI interfaces simplify configuration and access to debug and trace registers.

- Scalable Multi-Core Support: Debug and trace multiple RISC-V cores concurrently with independent control and status monitoring.

- SoC-Optimized Design: Low silicon overhead and power-efficient architecture, ideal for embedded and SoC environments.

- Optional Trigger Integration: Integrate with hardware triggers for precise, event-driven trace capture.

- Faster Development Cycles: Reduce debug iterations and simplify post-silicon validation to accelerate time to market.

- Highly Configurable: Configurable triggers, filters, and feature sets to match your SoC’s exact requirements.

- Fully Verified IP: Extensively verified to ensure predictable behavior and low integration risk.

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is RISC-V Debug & Trace IP?

RISC-V Debug & Trace IP is a CPU IP core from 10xEngineers listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.